# University of Sussex

#### A University of Sussex DPhil thesis

Available online via Sussex Research Online:

http://sro.sussex.ac.uk/

This thesis is protected by copyright which belongs to the author.

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Please visit Sussex Research Online for more information and further details

## Verification and Validation of complex vetronic systems with FlexRay

**Daniel Summers**

Submitted for the degree of Doctor of Philosophy

Department of Engineering and Design

School of Science and Technology

University of Sussex

September 2010

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification at this or any other university of other institute of learning.

The work in chapters 4, 5 and 6 is based on extending the MilCAN testbed, which was developed by P. Charchalakis and G. Valsamakis. In this thesis, MilCAN–related sections are present so that the design process leading to the development of the V&V testbed is coherent and complete. The FlexRay segment was developed by the author, and the TTP segment was developed by J.I. Melentis, another member of the research group in which this investigation was conducted. Therefore, information relevant to the TTP segment and its integration will not be shown in this thesis, unless it is deemed necessary for clarification or comparison. Additionally, the bridging and triggering systems detailed in this thesis are joint works conducted by I. Melentis, P. Charchalakis and the author.

This work was sponsored by the United Kingdom Ministry of Defence.

Copyright ©2010 Daniel Fraser Summers

ALL RIGHTS RESERVED

#### Abstract

Modern military vehicles have been retrofitted to contain a considerable number of embedded electronic subsystems of varying size and complexity over their operational lifespan, and many of these subsystems are interconnected by a variety of embedded networks. Upcoming next-generation vehicles will be designed with such networks and embedded subsystems built in from the day they are manufactured. When multiple subsystems and networks are present, it is often possible to benefit from integrating those networks and sharing information between systems.

Historically, however, integrating dissimilar embedded networks is a complex problem: it is not possible to certify a network composed of multiple different networking systems, and interactions between deterministic, safety–critical and non–real–time networks risk compromising the essential properties of one or more of them. Some form of integration testbed would likely simplify the process, along with an associated methodology.

This thesis details the development of such an integration testbed: its abstract design, mapping to implementing technologies and functional testing. The testbed is designed to be used in support of the V–Model (and similar testing–driven development methodologies) as a platform for development and verification testing of new and upgraded components and systems. As such, the testbed can be configured to simulate the target platform network and new components integrated and tested on it, then installed on the target platform with a minimum of additional effort.

#### Acknowledgements

I would like to thank my supervisor, Dr Elias Stipidis, for his guidance, patience and support during the research supporting this thesis.

I would also like to thank my second supervisor, Dr Falah Ali, and my colleagues and friends in the Vetronics Research Centre: in no particular order Dr Periklis Charchalakis, Dr Ian Colwill, Dr Obowoware Obi, Panos Oikonomidis, Dr Georgios Valsamakis, Dr Matthew Fowler, Dr Ireri Ibarra and Ioannis Melentis.

Finally, for acting as an anchor in the unpredictable tumult that has been the last five years of my life, I would like to thank my family and friends, in particular Yvonne and Christian Summers, Fouad Sethna, Rachael Acks, the Wayward Scholars and the denizens of #maelfroth and #afp.

Dedicated to the memory of Eileen Hewett and Frank Summers. Gone, but not forgotten.

## Contents

| Declara   | tion    |                                  |   |   |   |   | ii    |

|-----------|---------|----------------------------------|---|---|---|---|-------|

| Abstrac   | et      |                                  |   |   |   |   | iii   |

| Acknov    | vledgem | nents                            |   |   |   |   | iv    |

| Table of  | f Conte | nts                              |   |   |   |   | v     |

| List of ] | Figures |                                  |   |   |   |   | xi    |

| List of A | Acrony  | ms and Abbreviations             |   |   |   |   | xiv   |

| 1 Intr    | oductio | n                                |   |   |   |   | 1     |

| 1.1       | Mode    | rn Military Vetronics            | • | • | • | • | <br>1 |

|           | 1.1.1   | Trends in Vetronic Complexity    |   |   |   | • | <br>1 |

|           | 1.1.2   | Standards and Guidelines         |   |   |   | • | <br>2 |

|           | 1.1.3   | Certification                    |   |   |   | • | <br>3 |

| 1.2       | Embeo   | dded Systems                     |   |   |   | • | <br>4 |

|           | 1.2.1   | Introduction to Embedded Systems |   |   |   | • | <br>4 |

|           | 1.2.2   | A Proliferation of Platforms     |   |   |   | • | <br>5 |

|           | 1.2.3   | Real–Time Devices                |   |   |   | • | <br>6 |

|           | 1.2.4   | Determinism                      | _ |   |   |   | <br>7 |

|   | 1.3  | Resear   | ch Goals                                                                    | 7  |

|---|------|----------|-----------------------------------------------------------------------------|----|

|   | 1.4  | Achiev   | vements                                                                     | 10 |

|   | 1.5  | Thesis   | Outline                                                                     | 11 |

| 2 | Real | l Time H | Embedded Systems                                                            | 12 |

|   | 2.1  | Fieldbu  | uses                                                                        | 12 |

|   |      | 2.1.1    | Fieldbus Overview                                                           | 12 |

|   |      | 2.1.2    | Topology                                                                    | 14 |

|   |      | 2.1.3    | Triggering                                                                  | 20 |

|   |      | 2.1.4    | Segmentation and Bridging                                                   | 21 |

|   |      | 2.1.5    | Example Fieldbus: CAN                                                       | 23 |

|   |      | 2.1.6    | Application Layer Concerns in CAN                                           | 26 |

|   | 2.2  | Safety-  | -Critical Systems                                                           | 27 |

|   |      | 2.2.1    | Safety–Critical Concepts                                                    | 27 |

|   | 2.3  | X–By–    | -Wire                                                                       | 33 |

|   |      | 2.3.1    | Fly-by-Wire                                                                 | 34 |

|   |      | 2.3.2    | Drive-by-Wire                                                               | 36 |

| 3 | Stan | darde    | Guidelines and Methodologies                                                | 38 |

| 5 |      | ,        |                                                                             |    |

|   | 3.1  | Techni   | cal Considerations                                                          |    |

|   |      | 3.1.1    | Packet Size and Payload                                                     | 38 |

|   |      | 3.1.2    | Timings                                                                     | 40 |

|   |      | 3.1.3    | Latencies                                                                   | 40 |

|   |      | 3.1.4    | End-to-End Delays                                                           | 41 |

|   |      | 3.1.5    | Translation / Encapsulation / Association of messages and functionalities . | 41 |

|     | 3.1.6    | Addressing: Network–Node / –Bridge identification                                      | 43 |

|-----|----------|----------------------------------------------------------------------------------------|----|

|     | 3.1.7    | Synchronous / Asynchronous Operation                                                   | 44 |

|     | 3.1.8    | Absolute Time                                                                          | 45 |

|     | 3.1.9    | Technology–Independent Bridging                                                        | 46 |

|     | 3.1.10   | Commands that generate Information                                                     | 46 |

|     | 3.1.11   | Message Filtration                                                                     | 46 |

| 3.2 | VSI St   | andards and Guidelines                                                                 | 47 |

|     | 3.2.1    | Reduced Life–Cycle Costs                                                               | 48 |

|     | 3.2.2    | Modularity                                                                             | 49 |

|     | 3.2.3    | Distributed Architecture                                                               | 49 |

|     | 3.2.4    | Rapid Modification                                                                     | 50 |

|     | 3.2.5    | NEC                                                                                    | 50 |

|     | 3.2.6    | Recommended Standards (summary)                                                        | 51 |

|     | 3.2.7    | Middleware                                                                             | 52 |

| 3.3 | Develo   | ppment Methodologies                                                                   | 53 |

|     | 3.3.1    | Code and Fix                                                                           | 53 |

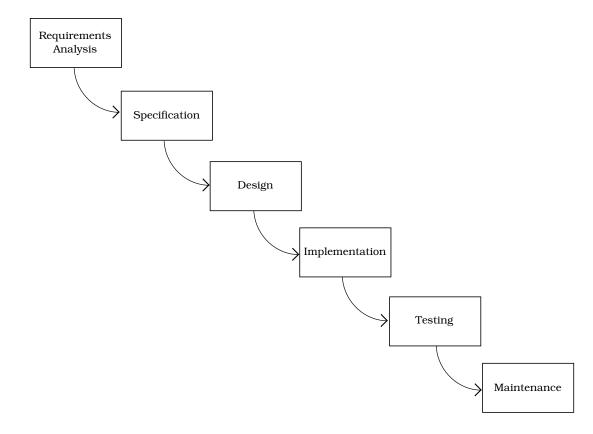

|     | 3.3.2    | The Waterfall Model                                                                    | 54 |

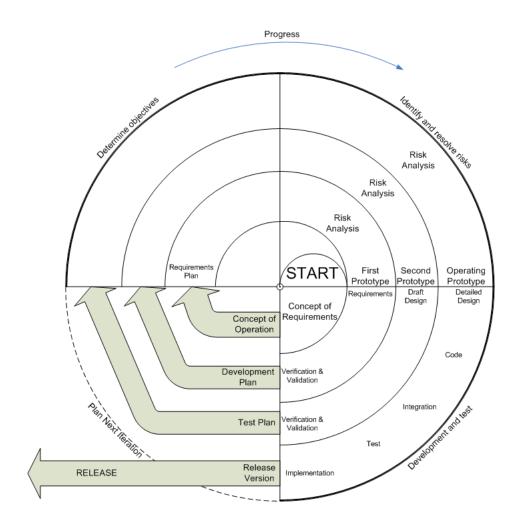

|     | 3.3.3    | The Spiral Model                                                                       | 56 |

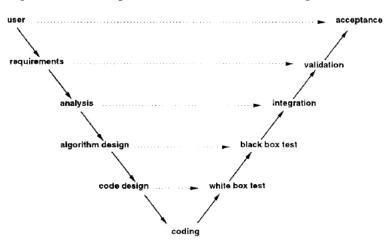

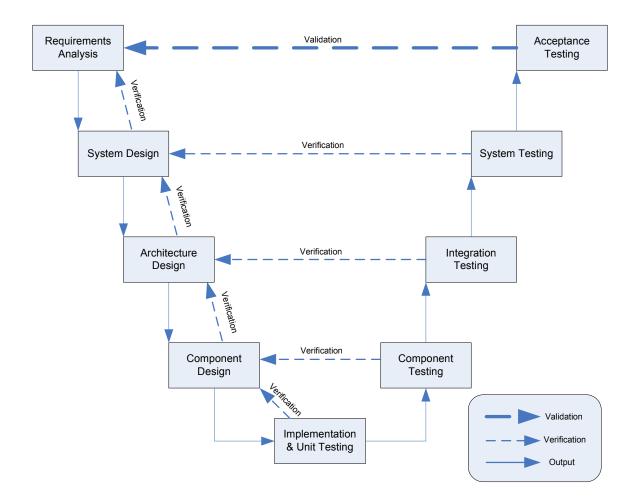

|     | 3.3.4    | The V–Model                                                                            | 57 |

| V&V | V Testbe | ed - Abstract Design                                                                   | 63 |

| 4.1 | Introdu  | $\alpha$ ction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 63 |

| 4.2 | Initial  | Considerations $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 63 |

|     | 4.2.1    | Technology Independence                                                                | 54 |

4

|   |             | 4.2.2   | Methodologies                   | 65 |

|---|-------------|---------|---------------------------------|----|

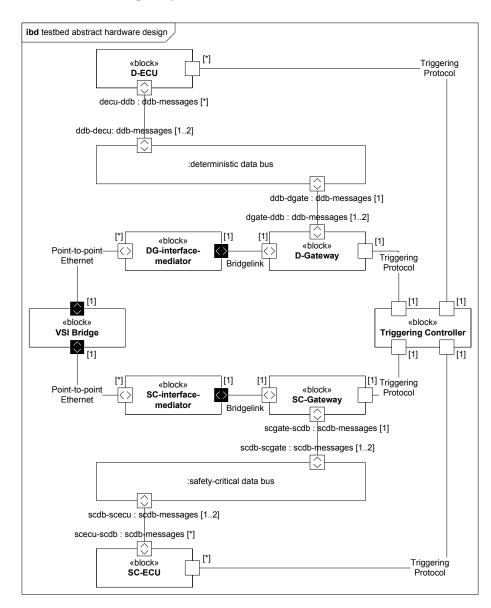

|   |             | 4.2.3   | Testbed Abstract Design (SysML) | 65 |

|   | 4.3         | Applic  | ation Networks                  | 66 |

|   |             | 4.3.1   | Hardware Design                 | 66 |

|   |             | 4.3.2   | Software Design                 | 68 |

|   | 4.4         | Trigge  | ring                            | 68 |

|   |             | 4.4.1   | Triggering Hub                  | 68 |

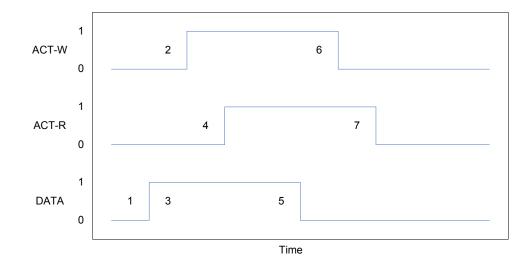

|   |             | 4.4.2   | ECU Triggering                  | 70 |

|   | 4.5         | Bridgi  | ng                              | 73 |

|   |             | 4.5.1   | Overview                        | 73 |

|   |             | 4.5.2   | Bridgelink Network Layer        | 73 |

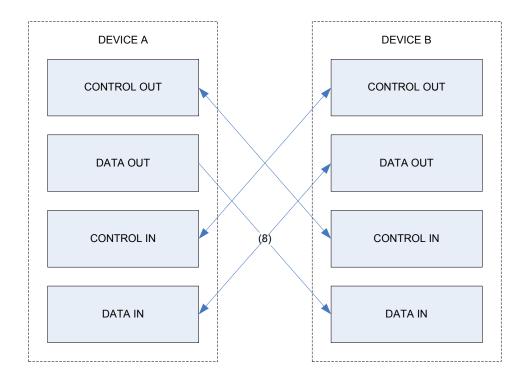

|   |             | 4.5.3   | Bridgelink Data–Link Layer      | 76 |

|   |             | 4.5.4   | Bridgelink Physical Layer       | 81 |

|   | 4.6         | Conclu  | ision                           | 84 |

| 5 | <b>V 8.</b> | V Tooth | ed - Technology Mapping         | 85 |

| 3 |             |         |                                 |    |

|   | 5.1         | Introdu | uction                          | 85 |

|   | 5.2         | Techno  | blogy Mapping – Overview        | 85 |

|   | 5.3         | Detern  | ninistic Network – MilCAN       | 86 |

|   |             | 5.3.1   | Protocol                        | 87 |

|   |             | 5.3.2   | Network Structure               | 88 |

|   |             | 5.3.3   | Development Kits                | 89 |

|   |             | 5.3.4   | High–Level Application          | 90 |

|   | 5.4         | Safety  | -Critical Network – FlexRay     | 91 |

|   |     | 5.4.1                                                                                                                 | Protocol                                                                                                                                | 92                                                                                                                 |

|---|-----|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|   |     | 5.4.2                                                                                                                 | Network Structure                                                                                                                       | 93                                                                                                                 |

|   |     | 5.4.3                                                                                                                 | Development Kits                                                                                                                        | 95                                                                                                                 |

|   |     | 5.4.4                                                                                                                 | High–Level Application                                                                                                                  | 98                                                                                                                 |

|   | 5.5 | Trigge                                                                                                                | ring                                                                                                                                    | 100                                                                                                                |

|   |     | 5.5.1                                                                                                                 | Management Node                                                                                                                         | 100                                                                                                                |

|   |     | 5.5.2                                                                                                                 | ECU Interface                                                                                                                           | 102                                                                                                                |

|   |     | 5.5.3                                                                                                                 | Operating Procedure                                                                                                                     | 103                                                                                                                |

|   | 5.6 | Proof                                                                                                                 | of Concept                                                                                                                              | 104                                                                                                                |

|   |     | 5.6.1                                                                                                                 | CAN proof-of-concept                                                                                                                    | 105                                                                                                                |

|   | 5.7 | Conclu                                                                                                                | usion                                                                                                                                   | 107                                                                                                                |

| 6 | V&V | V Testbo                                                                                                              | ed - Testing                                                                                                                            | 108                                                                                                                |

|   | 6.1 | Initial                                                                                                               | Configuration (Bridgelink)                                                                                                              | 109                                                                                                                |

|   |     | IIIIuai                                                                                                               |                                                                                                                                         | 107                                                                                                                |

|   |     | 6.1.1                                                                                                                 | Testbed Configuration                                                                                                                   |                                                                                                                    |

|   |     |                                                                                                                       |                                                                                                                                         | 109                                                                                                                |

|   |     | 6.1.1                                                                                                                 | Testbed Configuration                                                                                                                   | 109<br>111                                                                                                         |

|   |     | 6.1.1<br>6.1.2                                                                                                        | Testbed Configuration       Testing Protocol                                                                                            | 109<br>111<br>112                                                                                                  |

|   | 6.2 | <ul><li>6.1.1</li><li>6.1.2</li><li>6.1.3</li><li>6.1.4</li></ul>                                                     | Testbed Configuration                                                                                                                   | 109<br>111<br>112<br>116                                                                                           |

|   | 6.2 | <ul><li>6.1.1</li><li>6.1.2</li><li>6.1.3</li><li>6.1.4</li></ul>                                                     | Testbed Configuration   Testing Protocol   Results   Analysis                                                                           | 109<br>111<br>112<br>116<br>118                                                                                    |

|   | 6.2 | <ul> <li>6.1.1</li> <li>6.1.2</li> <li>6.1.3</li> <li>6.1.4</li> <li>Final C</li> </ul>                               | Testbed Configuration   Testing Protocol   Results   Analysis   Configuration (Ethlink)                                                 | 109<br>1111<br>112<br>1116<br>1118<br>1118                                                                         |

|   | 6.2 | <ul> <li>6.1.1</li> <li>6.1.2</li> <li>6.1.3</li> <li>6.1.4</li> <li>Final C</li> <li>6.2.1</li> </ul>                | Testbed Configuration   Testing Protocol   Results   Analysis   Configuration (Ethlink)   Testbed Configuration                         | <ol> <li>109</li> <li>111</li> <li>112</li> <li>116</li> <li>118</li> <li>118</li> <li>125</li> </ol>              |

|   | 6.2 | <ul> <li>6.1.1</li> <li>6.1.2</li> <li>6.1.3</li> <li>6.1.4</li> <li>Final C</li> <li>6.2.1</li> <li>6.2.2</li> </ul> | Testbed Configuration   Testing Protocol   Results   Analysis   Configuration (Ethlink)   Testbed Configuration   Testbed Configuration | <ol> <li>109</li> <li>111</li> <li>112</li> <li>116</li> <li>118</li> <li>118</li> <li>125</li> <li>126</li> </ol> |

#### 7 Conclusions & Further Work

| 7.1 | Conclu | uding Remarks                   |

|-----|--------|---------------------------------|

|     | 7.1.1  | The V&V Testbed                 |

|     | 7.1.2  | Challenges Met                  |

|     | 7.1.3  | TTP & FlexRay                   |

| 7.2 | Furthe | r Work                          |

|     | 7.2.1  | Alternate Technology Mappings   |

|     | 7.2.2  | Upgraded Triggering System      |

|     | 7.2.3  | Generic Vehicle Architectures   |

|     | 7.2.4  | Possible Future Vehicle Systems |

|     |        |                                 |

#### **References & Bibliography**

138

## **List of Figures**

| 2.1 | Passive Bus topology                                        | 16 |

|-----|-------------------------------------------------------------|----|

| 2.2 | Tree topology                                               | 17 |

| 2.3 | Passive Star topology                                       | 17 |

| 2.4 | Active Star topology                                        | 18 |

| 2.5 | Redundant Active Star topology                              | 19 |

| 2.6 | Cascaded Active Star topology                               | 20 |

| 2.7 | ISO11898 CAN Topology (from page 15 of [10])                | 24 |

| 2.8 | Basic (CAN–A) and Extended (CAN–B) frame formats            | 26 |

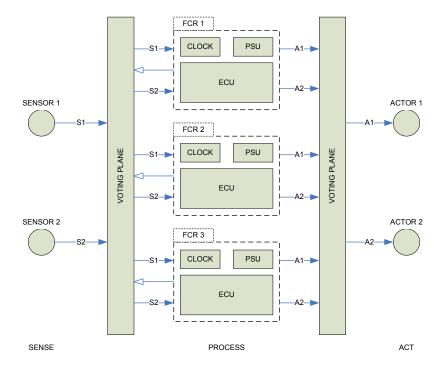

| 2.9 | An example replicated system with fault–containment         | 30 |

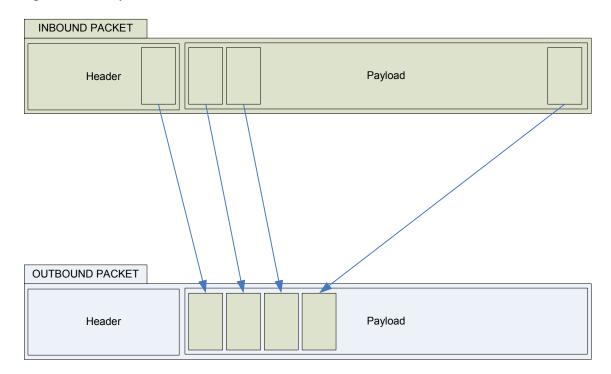

| 3.1 | Translation of packets                                      | 41 |

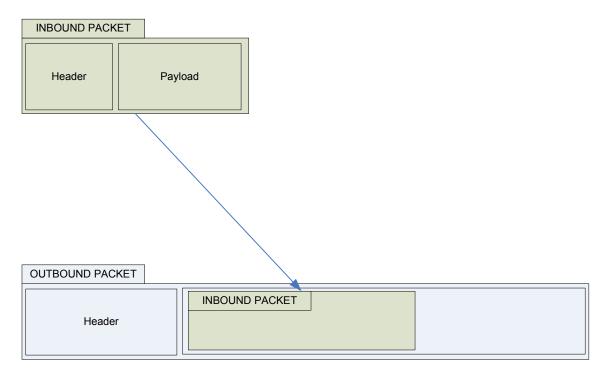

| 3.2 | Encapsulation of packets                                    | 42 |

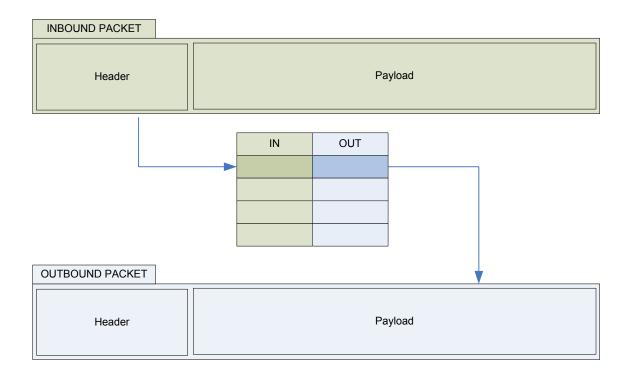

| 3.3 | Association of packets                                      | 43 |

| 3.4 | The Waterfall Model                                         | 54 |

| 3.5 | The Spiral Model, based on the diagram in [18]              | 58 |

| 3.6 | The V–Model from Hesselink, 1995 [20]                       | 58 |

| 4.1 | Internal Block Diagram showing the structure of the testbed | 65 |

| 4.2 | The Hybrid V–Model                                          | 67 |

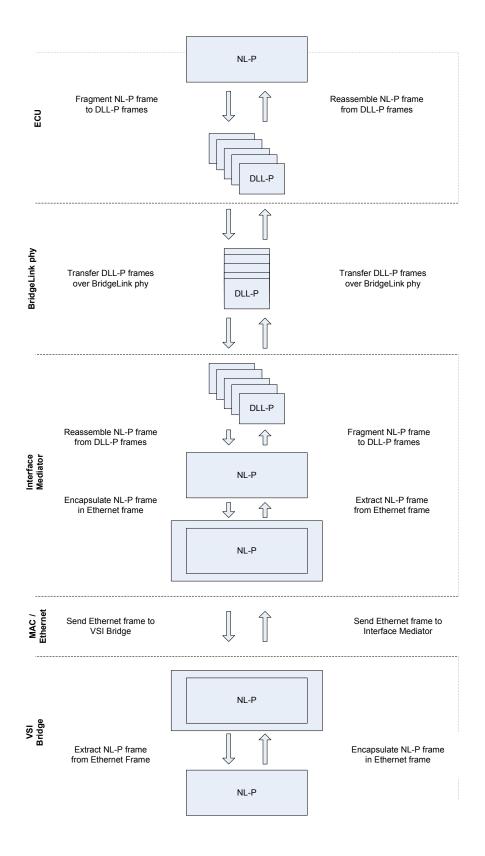

| 4.3 | BridgeLink sequence of operations                           | 74 |

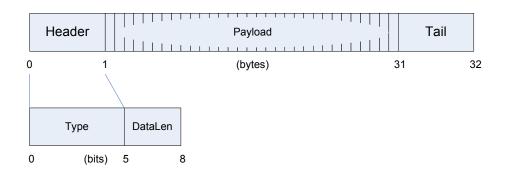

| 4.4  | The NL–P frame structure                                                                          |

|------|---------------------------------------------------------------------------------------------------|

| 4.5  | DLL–P frame layout                                                                                |

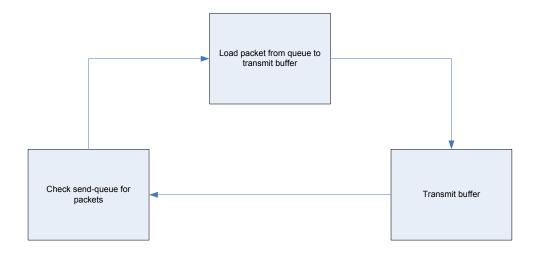

| 4.6  | The algorithm responsible for DLL–P frame transmission                                            |

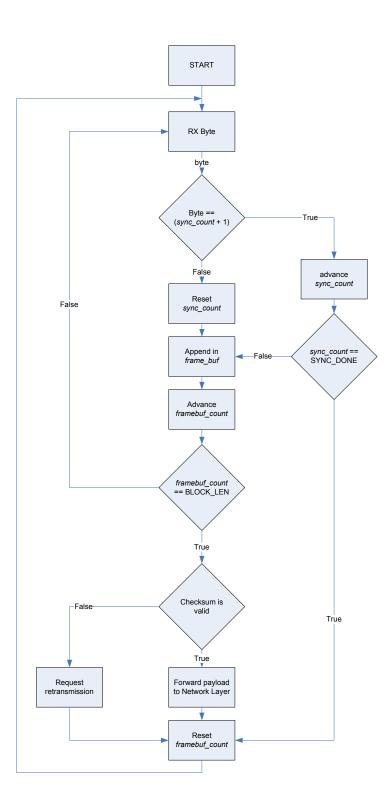

| 4.7  | The algorithm responsible for DLL–P frame reception                                               |

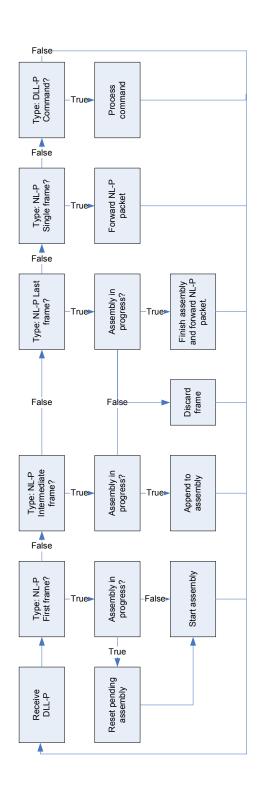

| 4.8  | The algorithm responsible for NL–P frame assembly                                                 |

| 4.9  | The physical-layer design for the BridgeLink protocol                                             |

| 4.10 | A unidirectional byte transfer using the BridgeLink protocol                                      |

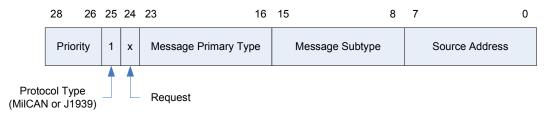

| 5.1  | MilCAN Message Identifier Layout (p24 of [24])                                                    |

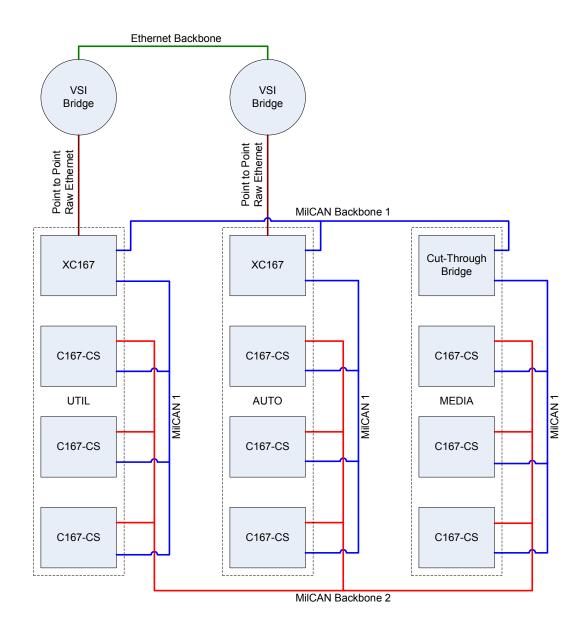

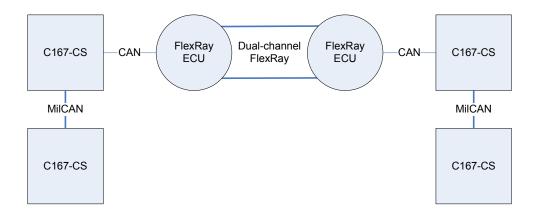

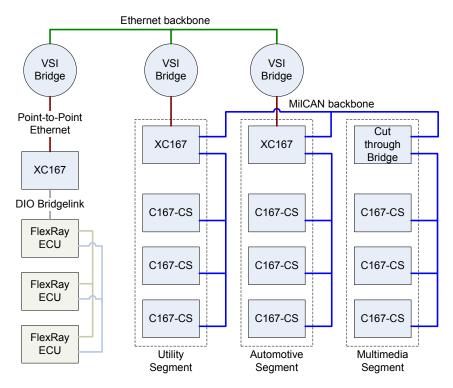

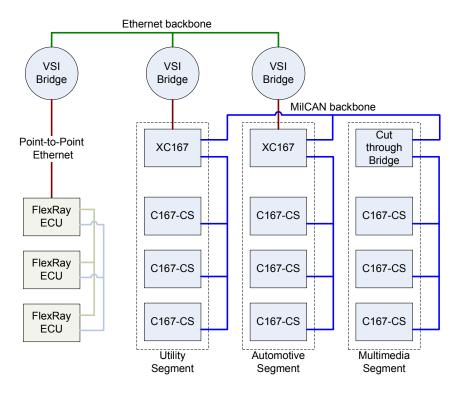

| 5.2  | Simplified diagram of the MilCAN segment                                                          |

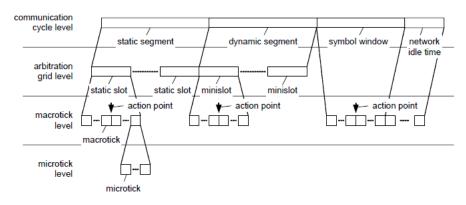

| 5.3  | FlexRay Communication Cycle structure (page 100 of the Protocol Specification,      [26])      92 |

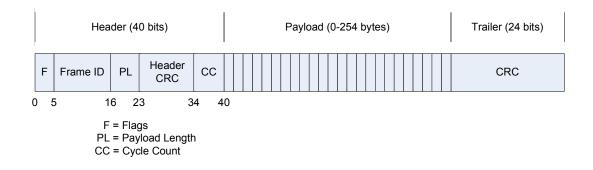

| 5.4  | FlexRay Frame structure                                                                           |

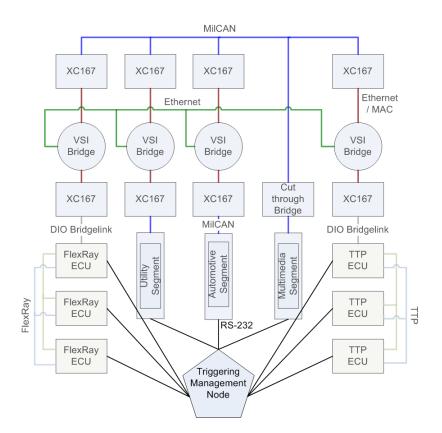

| 5.5  | VVV Testbed with triggering                                                                       |

| 5.6  | CAN proof of concept demonstrator                                                                 |

| 6.1  | First iteration of the Bridgelink testbed                                                         |

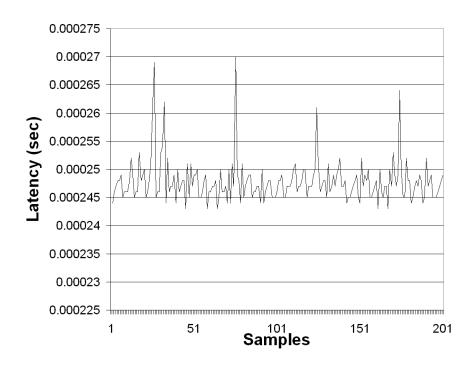

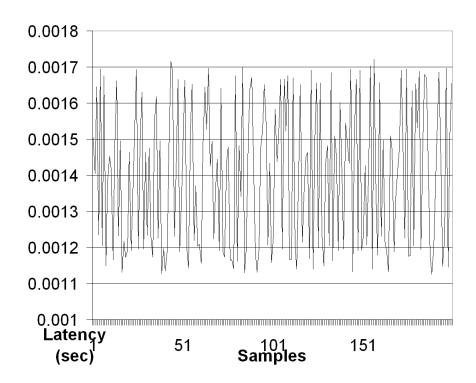

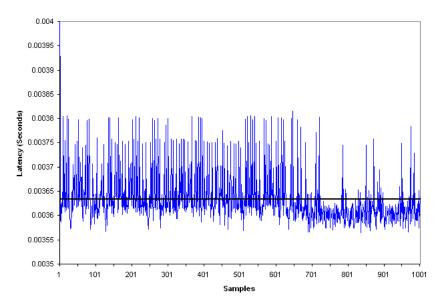

| 6.2  | Test 1.a. Loop latency from VSI Bridge host to XC167                                              |

| 6.3  | Test 1.b. Loop latency from VSI Bridge host to FlexRay gateway                                    |

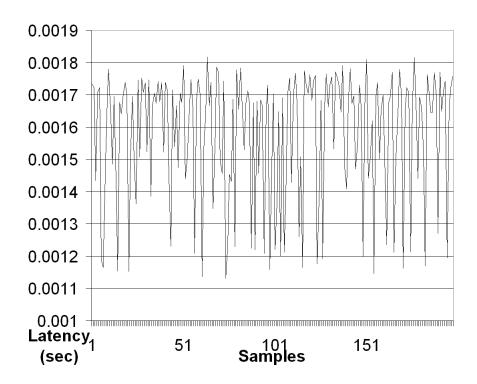

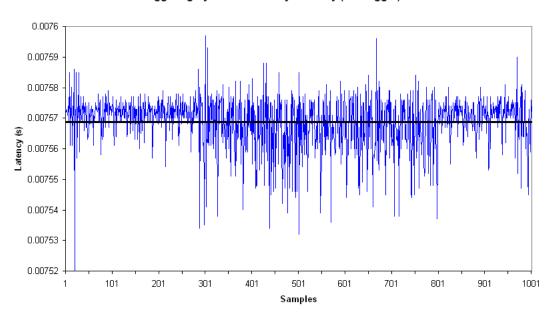

| 6.4  | Test 2.a. MilCAN loopback, via VSI Bridge host only                                               |

| 6.5  | Test 2.b. MilCAN loopback, with VSI Bridge software routing                                       |

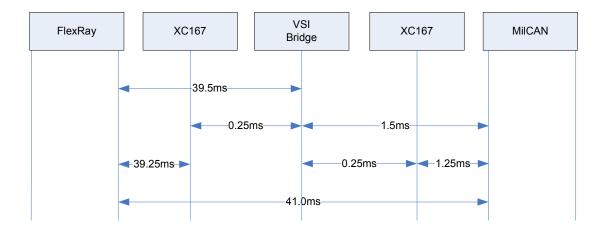

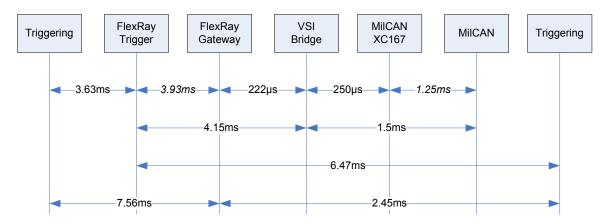

| 6.6  | FlexRay to MilCAN end to end round-trip average latencies breakdown                               |

| 6.7  | Final iteration of the Bridgelink testbed                                                         |

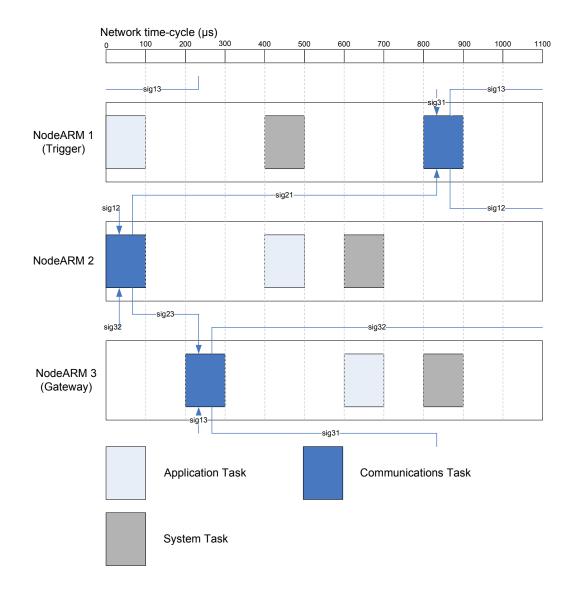

| 6.8  | Application skeleton for the FlexRay cluster                                                      |

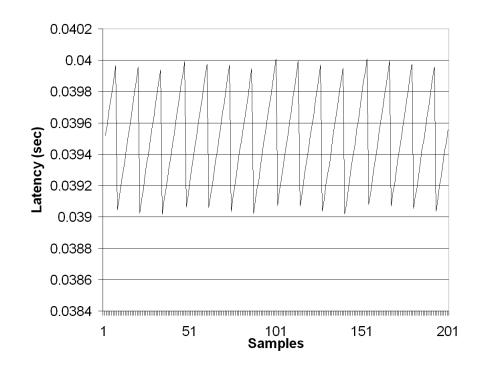

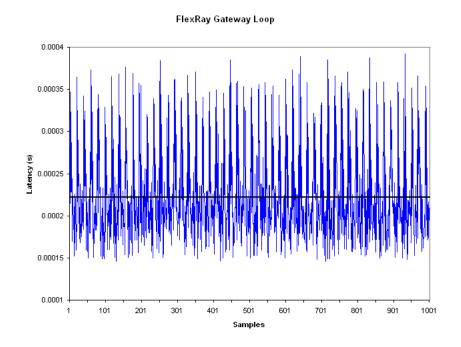

| 6.9  | VSI Bridge to FlexRay GW loopback                                                                 |

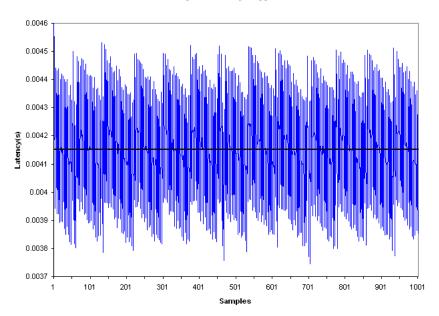

| 6.10 | VSI Bridge to FlexRay Trigger via Ethlink and FlexRay |

|------|-------------------------------------------------------|

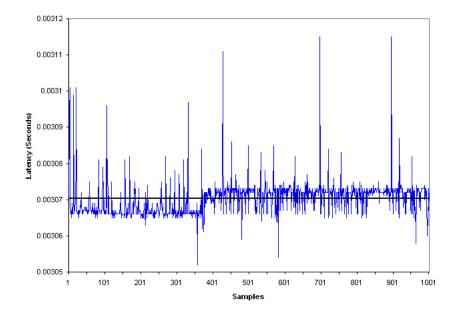

| 6.11 | Stimulus system direct loopback latency               |

| 6.12 | Triggering System latency - FlexRay Trigger           |

| 6.13 | Triggering System latency - FlexRay Gateway           |

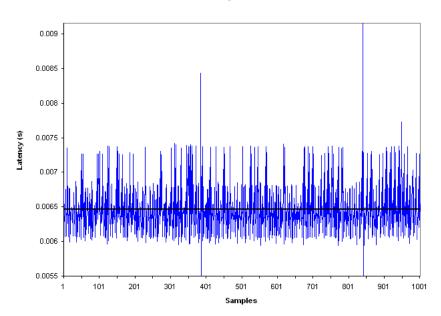

| 6.14 | MilCAN - FlexRay loopback                             |

| 6.15 | Consolidated timings for the FlexRay/MilCAN testbed   |

#### List of Acronyms and Abbreviations

- **AESTPI** Application Execution System and Target Platform Interface

- **API** Application Programmer's Interface

- ASSC Avionics Systems Standardisation Committee

- ABS Anti-lock Braking System

- CAN Controller–Area Network

- **CRC** Cyclic Redundancy Check

- **DLL** Data–Link Layer

- DLL-P Data–Link Layer Packet

- **DIO** Digital Input/Output

- ECU Electronic Control Unit

- **EMI** Electromagnetic Interference

- FCR Fault–Containment Region

- GVA Generic Vehicle Architecture

- HUMS Health & Usage Monitoring Systems

- HVAC Heating, Ventilation & Air Conditioning

- IEEE Institute of Electrical and Electronic Engineering

- ISTAR Intelligence, Surveillance, Target Acquisition and Reconnaissance

- **IP** Internet Protocol

- I/O Input/Output

- kbps kilobits per second

- LCD Liquid Crystal Display

- LIN Local Interconnect Network

- MAC Media Access Control

- MID Message IDentifier

- NEC Network Enabled Capability

- NL Network Layer

- NL–P Network Layer Packet

- **OBD-II** On-Board Diagnostics, version 2

- **OSI** Open Systems Interconnection

- PTU Primary Time Unit

- **RADAR** RAdio Detection And Ranging

- **RTR** Remote Transmission Request

- **RTAI** Real–Time Application Interface

- RTC Real–Time Clock

- TDMA Time–Driven Multiple Access

- TCP Transmission Control Protocol

- **TTP** Time–Triggered Protocol

- uint16 Unsigned 16–bit integer

- **USAF** United States Air Force

- V&V Verification and Validation

- VSI Vehicle Systems Integration

- YRL Yaw-Rate Limiter

## Chapter 1

## Introduction

#### **1.1 Modern Military Vetronics**

#### **1.1.1** Trends in Vetronic Complexity

Modern military vehicles contain an ever-increasing number of embedded electronic subsystems of various types and levels of complexity, and the trend shows no sign of slowing down. Current vehicles contain sensors, computers and communication equipment with capabilities far greater than those with which the vehicles were designed, some of which are linked with simple embedded networks to allow data exchange and information fusion. These electronic subsystems are commonly referred to collectively as "vetronics", a contraction of Vehicle Electronic Systems. Future vehicles will be developed with inbuilt control and sensing networks from the initial design, but are likely to undergo a similar process of upgrade and expansion over their service lifetime. Consequently, the process of designing new vehicles and components or subsystems is expected to continue to increase in complexity.

As combat doctrine continues to evolve towards a more information-centric view of the battlespace, and technologies such as ISTAR (Intelligence, Surveillance, Target Acquision and Reconnaissance) and integrated command and control systems become major components of military operations, western armies are becoming more and more dependent on electronic vehicle systems (for battlespace information, surveillance, telemetry and positioning, as well as functions such as fire control and intra– and inter–unit communication). Since these systems are becoming key to military operations, it is self–evident that they should be reliable and robust. Equally, however, they should be maintainable and extensible, in order to incorporate new technologies and address new threats as they become apparent. Military vetronics, then, is a complex and ever–changing field, and the challenge of developing a cost–efficient, reliable vehicle architecture that is sufficiently modular and extensible to serve in a modern army is a difficult one.

#### 1.1.2 Standards and Guidelines

The development process can, of course, be simplified by the provision of standardised processes and technologies. In the United Kingdom, Qinetiq have released a set of recommendations: the VSI (Vehicle Systems Integration) Standards and Guidelines [1] to guide the development process by offering advice on technology selection, recommended network architectures and device configuration. It is hoped that by following the Guidelines and implementing the Standards, device manufacturers and vehicle integrators will be able to increase the modularity, composability and maintainability of modern and next–generation military vehicles. The United Kingdom Ministry of Defence and Qinetiq are unusual in choosing to make such an effort: at present, no other armed force is attempting to specify open standard interfaces and architectures for military vehicles. The VSI programme is supported in part by the past work of my colleagues Dr Charchalakis [2] and Dr Valsamakis [3], among others.

The VSI Standards and Guidelines include recommendations on the use of multiple integrated networks, each one specialised to its task (safety–critical networks for vehicle drive– and fire–control, deterministic networks for internal management and sensor control, and high–bandwidth multimedia networks for video data, for example). A vehicle designed around these guidelines uses an appropriate network for each function, data being exchanged between them as necessary to report status or to manipulate properties of devices on other networks. Whether a network is "appropriate" for a given use is a function of its properties including available bandwidth, reliability, safety–criticality or determinism, complexity and (importantly) implementation cost. Since the inception of the VSI project (in June 2000), a great deal of investigation and research has been performed on the subject of vehicle systems integration and vetronics. On the 20th of August 2010, the UK MoD published DEF–STAN 23–09 [4], the Generic Vehicle Architecture (GVA). The GVA is a set of mechanical, electronic, power and interface specifications that all new military vehicles acquired by the UK MoD are required to implement. It recommends the use of open standard technologies and systems where possible, giving advice on integration methods and collecting together a variety of recommendations and DEF–STANs for choices of implementing technology in different areas of vehicle integration. The GVA DEF–STAN was not published until this thesis was almost ready for submission: it is included here to indicate the way in which vetronics standards are continuing to develop.

#### 1.1.3 Certification

Since the behaviour of the vehicle and its safe operation is strongly dependent on the correct operation of the vetronic systems, ensuring correct operation is of paramount importance. This can be done in simple systems by certification and testing, but as the number of protocols supported by a node and the number of network nodes in the system rises, it becomes increasingly impractical. Individual nodes on a given network can be certified as conforming to a given standard, as can simple segments in some cases, but the overall vetronics system cannot, as interactions between nodes tend to multiply with the square of the number of nodes. As the number of interactions between nodes (and within and across protocols and standards) increases, the certification process becomes intractable, as the number of variables that must be accounted for increases. To some extent, however, it is possible to certify the behaviour of a single network segment (composed as it is of a small number of certifiable nodes and a single communication standard), and then to connect certified networks together through carefully designed interconnectors. As a result, the production of an integration testbed on which individual subsystems can be tested and developed is of considerable interest. As well as allowing such testing and development, a testbed would also be useful for ongoing research into integration and complexity issues.

#### **1.2 Embedded Systems**

In this section, I will give a brief overview of the field of embedded systems, to ensure the reader is familiar with the terminology and concepts used later in this thesis.

#### **1.2.1** Introduction to Embedded Systems

In its most basic form, an Embedded System is a small microcontroller that, together with a group of connected sensors and actuators, performs a function. Embedded Systems can be found in a variety of applications in all areas of modern life, from the mobile telephone and the microwave, up to and including the control systems of a modern automobile or, at the extreme end of the scale, a nuclear power plant. In each case, the control functions are implemented primarily in the form of a set of software instructions (commonly referred to as "firmware", since it bridges the gap between *soft*ware and *hard*ware) running on the microcontroller or group of microcontrollers, taking into account signals from the sensors and driving the actuators accordingly.

In the case of a mobile telephone, the microcontroller is called upon to perform a large number of relatively simple tasks: encoding and decoding voice data using an appropriate codec, communicating that data with the cellular telephone system in its encoded form, receiving input from a keypad and displaying output on a small screen. In the case of a nuclear power station, the control functions tend to be more complex, and are consequently often implemented on a group of interconnected microcontrollers, so that each microcontroller can be dedicated to a part of the task and hopefully reduce the running time of the control algorithm by executing unrelated parts in parallel. It is relatively common for control functions to be implemented by a group rather than a single microcontroller, particularly in automotive and industrial control applications, where the sensors and actuators connected to the control system may be distributed over a significant physical range rather than close together.

If the control system is to be composed of a group of co–operating microcontrollers rather than a single device, it will need a communications system to carry data between its component units. This communications system will be required to carry user commands, sensor readings, state broadcasts and remote dispatch requests, and will operate in one of several modes depending on the type of data it is carrying and the type of system of which it is a part.

#### **1.2.2** A Proliferation of Platforms

A microprocessor is a general–purpose integrated circuit that reads instructions and data from a sequential memory structure, and manipulates the data according to the instructions. A typical microprocessor will be clocked in the hundreds to thousands of MHz range, have on–board memory management and floating–point acceleration, and require a set of support ICs such as both RAM and ROM, peripheral multiplexers and bus interface devices. A microcontroller is a simple microprocessor that reverses this arrangement: it will normally have memory and peripheral devices integrated in the same package, but tends not to support floating–point operations or complex memory management.

A microcontroller will typically include a range of integrated peripherals, commonly including analog–to–digital and digital–to–analog converters, pulse–width–modulation devices and communications modems for protocols such as CAN and LIN. Additionally, many will include several RS232 modems, both to connect to devices that use RS232 for control and to take commands from and give feedback to the user. A microcontroller will typically operate at a lower clock–speed than a microprocessor, commonly in the range from single unit MHz to a few hundred MHz. However, these speeds are quite sufficient for the embedded control applications in which microcontrollers are typically used, and result in a significantly lower power consumption than a microprocessor (as low as  $200\mu$ A in the case of some 1MHz Atmel AVR devices). This broad range of integrated peripherals, coupled with their minimal power consumption, means that a microcontroller is often the only silicon device needed to implement a simple process controller.

A broad variety of embedded communications systems exist, ranging from the simple (RS–232, RS–485) through the frame–based (CAN, LIN, simple Ethernet) and ending in the safety–critical systems (TTP-C, FlexRay). The simple systems typically provide a way to transfer bytewise data between two linked microcontrollers. More complex frame–based systems introduce the concept of addressing, allowing a single message to be transferred to a single target device on a network containing many, or to be broadcast to a group of devices. A frame–based system will normally allow larger "chunks" of data to be transferred: where a standard RS–232 messages is typically small, containing a single octet of data, frame based systems can be used to transfer several octets in a single message (ranging from a maximum payload size of 8 octets in a CAN message to approximately 1500 octets in an Ethernet frame). Finally, safety–critical communications systems will include additional data alongside the payload that is used to keep all units in the cluster syn-

chronised to a common timebase, maintain the logical structure of the cluster, and allow the content of the payload to be error–checked to ensure that it has not been corrupted in transit. The subject of embedded communications is discussed in more detail in section 2.1.

#### **1.2.3** Real–Time Devices

The great majority of microcontroller–based embedded systems (certainly those in process–control and automotive applications) can also be considered as "real–time" systems. A "real–time" system is one in which parameters such as communications latency, response time and worst–case execution time are tightly controlled (to take a simple example, an automotive steer–by–wire system requires a response time at or below the threshold of human perception, in the region of 10ms, to ensure safe and accurate operation).

Systems that can be considered "real-time" are normally classified as either *soft* or *hard* realtime. A hard real-time system is one in which continued correct function (and, potentially, operator safety) is strictly dependent upon the system performing within its designed response deadlines. Typically, hard-real-time constraints are found in areas where the system is interfaced at a low level with physical hardware of a timing-critical nature, such as industrial process control and in the automotive sector, as well as in medical technology such as nuclear-therapeutic and -diagnostic equipment. A soft real-time system, by contrast, will tolerate a certain amount of latency and deadline overrun, compensating where possible to stay close to the required timing. Soft-real-time systems can be found in areas such as video display systems (where it can be occasionally preferable to skip an entire frame than to slip progressively out of synchronisation with the audio track) and in operating system process management (where it may be more important that a process runs to completion than that other processes are serviced in a timely manner).

In order to provide real-time guarantees, the system should not be expected to operate at full capacity. A system loaded near its operational capacity may not be able to meet all its timing deadlines, due to resource contention or multi-tasking; it is common to see an 80% system load considered a safe maximum value.

#### 1.2.4 Determinism

A given system is defined as deterministic in addition to being "Real–Time" if its behaviour can be accurately predicted from its current state and its current inputs. This is a desirable property in many embedded systems, as it means that the timing properties of a variety of operations within the system can be measured, then used to generate an efficient schedule of operations such that the system performs its function at the maximum possible speed. A non–deterministic system being scheduled in the same way risks the variation in operation timing properties causing one or more operations to overrun, which is likely to result in at best degraded performance, at worst outright system failure.

As a single embedded system can be deterministic, so can an embedded network. Deterministic networking protocols tend to require a small amount of additional overhead, both in terms of data required in frames travelling the network and in the nodes communicating on the network (a deterministic networking stack typically requires timing and interrupt resources from the host to maintain real–time behaviour). If a deterministic network is presented with the same input frames at the same points in the time cycle, it will always deliver the frames in the same order (not necessarily the input order) and with the same delivery latency. It should be noted that when determining whether one frame is "the same as" another frame for the purposes of studying a deterministic network, the decision can be made solely on the basis of the routing and priority information assigned to that frame: differences in the payload should not affect delivery parameters. MilCAN is an example of a deterministic embedded networking protocol; see section 5.3.1 for more details.

#### **1.3 Research Goals**

As has been noted previously, the level of complexity of deployed vetronic systems continues to rise. A complex deployed system implies a complex design and a complex development process. However, this need not be the case: a suitable developmental methodology (accompanied by an appropriate testbed) can substantially reduce the design and development workload for a given project by providing a base on which to build.

It is, therefore, the overall goal of this thesis to document the design of an abstract vetronic networking testbed, which was then mapped on to a set of implementing technologies and tested for performance. It is hoped that this testbed and this example implementation will be a useful tool in the design and development of the next generation of vetronic networks and networked systems.

In order to be useful, the proposed testbed must exhibit certain features, at a minimum. It must contain at least one deterministic network segment, and at least one safety-critical network segment, since these networks are the most likely to present integration problems (integrating the majority of simple and frame-based networks is not difficult, as long as the network data is being transferred into has sufficient capacity to contain it, while deterministic and safety-critical networks have multiple other problems such as state maintenance, membership and timing). It must contain at least one programmable bridge device, capable of transferring messages from one network to another (ideally, every network segment will be connected to every other network segment, the connecting bridges being configured to block traffic by default). Finally, it must contain some form of measurement and monitoring system so that the behaviour of the segments composing the testbed can be manipulated to simulate one or more testing scenarios.

It is hoped that the methodology and testbed design resulting from this research will reduce the time necessary to develop vetronic systems, whether the system in question is a component to be added to an existing vehicle or a completely new vehicle architecture. This will be possible due to the way in which the testbed can be configured to simulate the behaviour of the other segments being developed: in the case of a new component or subsystem, it can simulate the dataflow to which that component or subsystem will be exposed in use, while in the case of a new network it can inject strategically chosen frames containing data to describe a testing scenario, and the response of the vetronic architecture to this scenario can be observed.

With an appropriately detailed specification, it will be possible to begin simulation testing comparatively early in the development process. This will result in a reduction in development risk (since flawed implementations should become apparent during early testing, before they become entrenched in the design). This reduction in risk will result in turn in a reduction in development time and development cost.

The existence of an integration testbed and methodology will simplify the development of segmented and service–oriented networks, as the segment under development can be connected to a simulation of the other segments in the vehicle. It is not necessary to develop the entire networked system monolithically, nor to maintain a complete hardware replica of the networked system for the purposes of testing the integration of new components. It should be noted, of course, that military projects often find civil applications and vice versa. Although the Verification and Validation (V&V) Testbed detailed in this thesis was developed under the auspices of the UK MoD, there is no reason why it could not be used to aid in the development of a civilian vehicle.

#### 1.4 Achievements

Modern vetronics networks continue to increase in complexity, as new devices and new features are added, both in the design stage and to finished vehicles. A vetronics network will often consist of multiple heterogeneous network segments, and the integration of these segments is desirable.

In the process of performing the research leading to this thesis, three main achievements were reached. They and their background will be explained in detail in the remainder of this thesis.

- Interfaces and procedure for integrating heterogeneous embedded networks were defined: in particular, for safety–critical and deterministic systems.

- An abstract vetronics testbed was produced, which can be configured to represent most vehicle networks, or act as a common reference during design and testing.

- An triggering and monitoring system was produced that allows performance and behavioural data to be gathered from the abstract testbed in a repeatable manner.

#### 1.5 Thesis Outline

- Chapter 2 provides an introduction to the technologies relevant to this thesis: fieldbuses and embedded networks, safety-critical systems and X-by-wire systems.

- **Chapter 3** provides an examination of the technical considerations that relate to the development of a network bridge, as well as presenting an introduction to the VSI Standards and Guidelines and to common development methodologies.

- **Chapter 4** is the first contribution chapter, and introduces the design of the V&V Testbed: the component network types, the triggering system and the essentials of the bridging system.

- **Chapter 5** is the second contribution chapter, giving the chosen technology mapping used to implement the abstract design in this research.

- **Chapter 6** is the third contribution chapter, presenting the results of a series of tests run, first on the testbed configuration described in chapters 4 and 5, and then on a slightly altered configuration that produces significantly better results.

- **Chapter 7** presents concluding remarks, as well as some suggestions for further work to investigate the properties of the testbed and to apply it to new technologies emerging in the field.

## Chapter 2

### **Real Time Embedded Systems**

#### Introduction

In this chapter, a brief overview of the field of embedded and safety–critical networking will be presented, touching on the key issues contained in each area and defining terms that will then be used in the rest of this thesis. There will be a discussion of fieldbus technology, including an example fieldbus (the Controller–Area Networking protocol), followed by a study of the concept and properties of a safety–critical system, including example applications.

#### 2.1 Fieldbuses

#### 2.1.1 Fieldbus Overview

Automotive electronics and aircraft electronics have followed a similar development path. In the case of aircraft, the mechanical pushrods and cables that once linked the pilot directly to the control surfaces and engines of the aircraft have been slowly replaced with more complex and featureful electronic links. In the case of cars, the mechanical links have been augmented over time with

electronic systems such as Anti-Lock Braking and Traction Control Systems, and it seems likely that electronic links will begin to replace the mechanical linkages in new vehicles in the near future. The presence of these systems, together with other electrical and electronic systems within the car such as HVAC, lighting, entertainment and navigation, means that the electrical and electronic complexity of a typical modern vehicle continues to increase (Albert, in 2004, noted that modern upper–class vehicles can contain up to 70 ECUs [5]

In 2002, Leen [6] notes that some modern high–end vehicles may have up to 4 kilometres of internal wiring. The reason for this is quite simple: in many cases, each electronic system uses dedicated cabling to carry data from input sensors and switches to output actuators, often via intermediate processors. This approach results in a considerable amount of effectively duplicated cable, running from adjacent switches on the control panel to adjacent actuators elsewhere in the vehicle. This duplication of cable adds a significant amount of weight and complexity to the vehicle. Additionally, it makes servicing and maintenance notably more difficult, as tracing and accessing a single cable in a multi–cable run becomes more challenging as the number of cables in the run increases.

Introducing a Fieldbus to the vehicle allows the complexity of cabling to be reduced without sacrificing the feature–set of the vehicle. In its simplest form, a fieldbus is a local–area network in which the local area is a vehicle rather than a building or a floor of a building. A traditional electronic control system would interconnect switches and actuators in a given subsystem with their controlling processor using dedicated cables. A fieldbus–based system, by contrast, will connect switches and actuators to physically local processors, which are then interconnected by a digital communications network. Control functions that would be based on a single processor may be handled on the processor responsible for controlling the relevant actuator, or by an intermediate processor. Instead of long sensor and actuator control cables being run to a central processor, a fieldbus system makes use of short sensor and actuator control cables and an increased number of processor will typically be responsible for multiple sensors and actuators, the complexity of the interconnect is decreased substantially.

It should be noted that the fieldbus concept is neither particularly new nor unique to the field of transport engineering: its original genesis was in the field of industrial process control, where fieldbuses such as Foundation Fieldbus and PROFIBUS were developed in the mid–1980s ([7],

[8]) to support production–line automation and error reporting. Functionally, industrial fieldbuses and vehicular buses are similar if not identical: in both cases they carry the data given to them according to a predefined schedule, it is merely the semantic meaning of the data that changes between applications.

If a metaphor is required, a fieldbus system can be seen as a public transport system for data. Instead of each subsystem of the vehicle having a dedicated transport system in the form of a cable link (or in this metaphor, a car), the fieldbus "picks up" data at the input point and carries it around the network, "dropping it off" at the output point. The analogy is imperfect because most fieldbuses are message-addressed rather than node-addressed (a message on the network has a message identifier, as opposed to source and destination addresses), so one message can be received by multiple nodes if its contents are of interest to them. In addition to simplifying cable routing, there is another potential benefit to the implementation of a fieldbus-based architecture: it becomes much simpler to add subsystems to the vehicle, as plugging new devices into the fieldbus and assigning them messages on the network is much simpler than finding a way to route yet another cable through congested cable-ways. In particular, the majority of fieldbus systems tend to implement some form of "composability", a property of the network that means that so long as two applications don't both write the same message IDs, they can coexist on the same network without interfering with each others' behaviour. When adding devices to a fieldbus in this manner, however, one must take care to ensure there is enough spare network capacity available to handle the new application.

The remainder of this section will discuss the properties of fieldbuses, in particular common Topologies used, Triggering methods (event triggering and time triggering) and the subject of Network Segmentation and Message Bridging.

#### 2.1.2 Topology

The Topology of a communications network is the arrangement of its nodes, relative to one another. A diagram of the topology of a network represents the interconnections between nodes and approximate distances between them. It does not represent the positions of the nodes in physical space, or the precise route that connecting cables take between them: it is a logical map, not a physical one. While the topology of a real–world network can be extremely complex, it will normally be possible to generalise it as one of the following examples, by aggregating nodes into subsystems and studying the system at a high level of abstraction (some less common topologies such as Ring and Daisy–Chain were not considered, since they are rarely seen in embedded networks).

#### **Multiple Channels**

A multiple–channel "topology" is not really a topology in and of itself: rather, most of the following network topologies can be built either single–channel (as shown in most of the diagrams) or multiple–channel (by replacing each single link with multiple parallel links). Introducing an additional channel to the network increases wiring complexity, but can result in significant benefits in terms of reliability or available bandwidth. It should, perhaps, be noted that the most common multiple–channel implementation is a dual–channel system.

If the two channels are redundant, carrying the same data, the reliability of the network is improved. The messages can be compared on arrival, and differences between messages that should be the same indicate a fault on one or other bus. In the simplest case, the receiver can request retransmission, or use the message checksum (if present) to select the undamaged message. If *both* messages are corrupted, a simple dual–channel system provides no benefit. However, it lays the ground for spatial and temporal redundancy (summarised below, and explained in more detail in section 2.2.1).

A multiple–channel redundant system in which the physical layer for each channel takes a different path through the vehicle or factory is spatially redundant. Damage to any one location is less likely to destroy the communications link, as the loss of one channel can be compensated for by the duplicate messages on the second channel. Alternatively, a multiple–channel system in which the same message is sent on different channels at different times is temporally redundant. Transient EMI and other faults that would otherwise damage all messages in the same way can be detected because the corruption occurs at different points in the different messages.

If the two channels are not redundant, a multiple–channel system allows the same topology to achieve a higher throughput rate, because messages can be sent on either channel. Assuming the nodes of the network are capable of producing and consuming messages at that rate, the multiple–channel system is capable of throughput up to the bandwidth of each channel multiplied by the number of channels. Equally, a second channel can be reserved for high–importance messages,

so that their transfer latency is not affected by the presence of other messages being transferred between nodes.

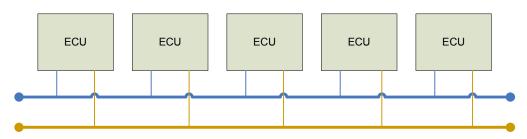

Figure 2.1: Passive Bus topology

The Passive Bus topology is simple and common. A communications bus is laid, and all nodes are connected to it directly. The communications bus will require termination resistors, but contains no further active components. Consequently, messages sent on the passive bus will be received by all connected nodes: it is necessarily a broadcast topology. The diagram in figure 2.1 depicts a dual–channel passive bus topology, as is often used in CAN networks.

Passive Bus systems are cheap and simple to build, requiring comparatively few components. Their broadcast nature, however, means that it is difficult to achieve high throughput when compared to topologies such as the active star. Controller–Area Networking development segments are commonly based on passive buses, as are FlexRay development networks, due to the comparative simplicity of wiring.

#### Tree

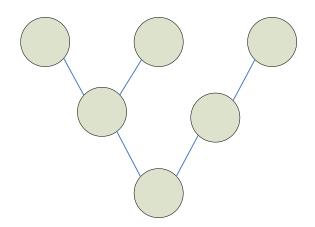

The Tree topology assumes that nodes within the network have multiple communications interfaces, and that messages can be forwarded over a succession of point-to-point links during their journey from source to destination. A network following the tree topology has a defined "root" node: nodes can then be classified into levels depending on how many links must be followed from them to reach the root node (the root node has level 0, nodes directly connected to it have level one, nodes connected to *them* have level 2, etc.). Additionally, a tree topology is said to have a "branching factor", defined as the average number of arcs connected to a node within the tree (by way of example, the topology depicted in figure 2.2 has a branching factor of 1.6).

Figure 2.2: Tree topology

A tree topology is said to be a "spanning tree" if every node can trace a connection from itself to the root, but there are no cycles (closed loops in the graph). In the case of a weighted tree (link weightings being assigned according to the domain: in networking, latency or bandwidth are common weighting factors), the spanning tree for which every node has the minimum possible cost for the route linking it to the root is called the "minimum spanning tree" for that tree.

The minimum spanning tree topology is common in enterprise networking, where the connection from a desktop computer to the backbone router may pass through a series of switched subnets en route. It is somewhat less common in embedded networking, where the majority of devices will be on the same subnet as the devices to which they communicate.

**Passive Star**

Figure 2.3: Passive Star topology

The Passive Star topology is more complex to construct than the Passive Bus, since it requires a central cable splice between individual node links. Like the passive bus, it contains no active

components, being nothing more than a wiring loom. Again, like the passive bus, the passive star is necessarily a broadcast topology, since there is nothing to prevent the signal from propagating along all branches of the star.

Ignoring the relatively minor complexity involved in building the central cable splice, a passive star topology has the same advantages and disadvantages as a passive bus topology.

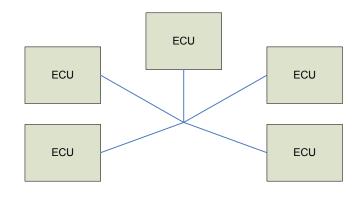

#### Active Star

Figure 2.4: Active Star topology

The Active Star topology is superficially similar to the Passive Star, but its electrical properties are notably different (it is, in fact, more similar to a Tree). Instead of a cable splice, the individual node links are connected to a central switching fabric that broadcasts a message received from a given branch to all other branches. The central star coupler regenerates passing signals, and can optionally filter incoming messages such that they are broadcast only to nodes that declare an interest in the content of the message.

The central star coupler introduces additional complexity and cost into the network design, but it also improves signal quality (reducing corruption and retransmission) and allows for the possibility of message filtration, potentially increasing the maximum available bandwidth (if two messages have different source and destination nodes and the star coupler has sufficient capacity, they can occupy the network simultaneously as they need never share resources).

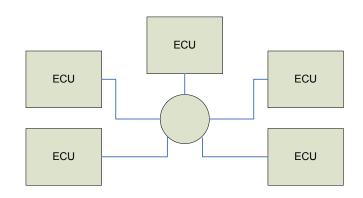

#### **Redundant Active Star**

The simplest form of a redundant active star network is a two-channel network in which each node has two communications interfaces, each interface connected to a different active star coupler (for

Figure 2.5: Redundant Active Star topology

a total of two star couplers, one per channel). Such a network is depicted in figure 2.5, and is often used in production FlexRay networks.

There are several possible benefits to network redundancy. A network is said to replicate another network if it contains the same messages at every point in time (being effectively a synchronised copy of the first network). If the two networks replicate each other, then physical damage or failure of one network will not compromise the ability of the cluster to transport messages between the ECUs that comprise it. It is possible to further mitigate the effects of damage on the network by routing the redundant cables through different physical areas, so that damage to one does not affect the other without having also terminally damaged one or more nodes in the process. The principle of redundancy in network design is further discussed later in this thesis, in section 3.2.3.

If the two networks do not replicate each other, the potential bandwidth of the cluster is doubled, as messages are no longer transmitted on both networks, meaning that it is possible to transmit two different messages at the same time, one on each network.

Multiplying the number of star couplers and associated link cables increases the cost of implementation in a more or less linear manner, but the benefits of doing so tend to be reduced once the number of redundant networks passes low unit numbers.

#### **Cascaded Active Star**

A Cascaded Active Star is a non-redundant configuration containing a single channel, but multiple active star couplers. Each node in the network is connected to one star coupler, and the star couplers themselves are connected together, resulting in a spanning tree. The configuration in

Figure 2.6: Cascaded Active Star topology

figure 2.6 has three nodes connected to one star coupler and two nodes connected to the other (in implementations, the link connecting the star couplers will often be set to operate at a higher bandwidth than the links on the periphery, reducing congestion at the couplers).

The Cascaded Active Star topology is more expensive in both cost and complexity than a single active star, but provides the potential benefit that it is possible to partition the network physically but not logically, using a single (or a small number) of "backbone" connections to link islands of nodes together, each with its own local star coupler. It should be noted, however, that each Active Star Coupler on a link between two nodes will add an additional overhead in terms of transmission time, as each Active Star must at least process and regenerate the signal, and may optionally take additional time to filter it and rebroadcast only on certain channels.

#### 2.1.3 Triggering

In addition to the topology of the network, it is important to consider how it is triggered when studying its properties. Where topological design and cable length make it possible to estimate network bandwidth and latency arising from hardware concerns, triggering makes it possible to consider unavoidable protocol delays as well.

The triggering procedure for a network indicates how messages held in node transmission buffers are dispatched on to the bus. There are two common triggering procedures used in embedded networks: event triggering and time triggering. Both are explained briefly below.

#### **Event-Triggered Networks**

In an event triggered network, each node will attempt to transmit messages as soon as the application running on the node requests transmission. Exactly when the message is transmitted will depend on the collision resolution procedure of the protocol in use and network load, but it will be sent as soon as reasonably possible.

Event triggered designs have the advantage that messages always tend towards the minimum possible latency for the network conditions in which they operate. However, since there is no control over delivery times, messages can easily arrive out of order and, in heavily loaded networks, with significant delays (due to large numbers of other messages winning collision resolution against them before transmission is successful).

#### **Time-Triggered Networks**

In a time triggered network, there exists a global schedule that allocates periodic time slots to messages. A copy of this schedule is normally present on each node, and each node has a view of the global timebase, whether synchronised by a timekeeping master node or by group agreement. A message may then only be transmitted in its allocated time slot.

Time triggered networks are highly deterministic: it is possible to predict which message will be present on the bus at a given time with a high degree of accuracy. However, because messages must wait for their next scheduled slot before being dispatched on to the bus, a degree of additional latency is unavoidable (the exact amount of delay applied to each message being dependent on the current state of the schedule and the time remaining until an appropriate slot is available). Messages should never be lost in a properly scheduled time triggered network, as each message is assigned to a slot of appropriate length.

# 2.1.4 Segmentation and Bridging

The availability of spare network capacity can be a serious problem in non-trivial networks. A typical modern vehicle network includes a large number of systems and controllers, including (but not limited to) the following:

• Power-train controllers

- HVAC (Heating, Ventilation and Air–Conditioning)

- Navigation subsystems

- ABS (Anti-lock Braking System)

- Traction–Control subsystems

- Engine-management computers

- Security systems such as central locking and immobilisers

- HUMS (Health and Usage Monitoring Systems)

- Entertainment systems (radio, video screens in some high–end models, etc.)

When the communications requirements of all these systems and controllers are considered together, it is commonplace for the required network bandwidth and availability to be in excess of that which the backbone network is capable of supplying.

It is normally possible to reduce the communications requirements of the fieldbus network by splitting it into several functional segments, such that all the devices relevant to a particular function are connected exclusively to a single segment. This has the effect of confining the bandwidth load associated with a particular task or subsystem to a single network segment, reducing global network bandwidth usage and frame latency. In addition, this segmentation can have an effect not unlike modular abstraction in computer programming, forcing clear interfaces between components of the overall system of systems and making it simpler to add new subsystems to the network. One popular segmentation scheme divides the network into three segments: Automotive (containing systems such as power–train, ABS and Traction Control), Multimedia (radio, communications) and Utilities (navigation, diagnostics, HUMS, HVAC).

Although segmenting the network in this way results in a significant reduction in required network bandwidth and availability, it has its drawbacks in that it restricts data flow between seemingly unrelated systems (the obvious example in the segmentation scheme above being that the diagnostics subsystem is unable to receive diagnostic data from the power-train). The compromise solution is to perform functional segmentation as directed above, then connect the segments together by adding intelligent network bridges: devices with multiple network interfaces that transfer data between segments according to a set of mutable rules. In this way, vital data (such as diagnostics and error-reporting) can be moved between segments without overloading any segment with data irrelevant to its function.

#### 2.1.5 Example Fieldbus: CAN

# Introduction

CAN, the Controller Area Network, is a more complex fieldbus originally designed for use in automotive applications, although it has now spread into the fields of industrial automation and medical equipment. A CAN network does not have a master-slave architecture: all nodes are equal, and message collisions are avoided by bitwise arbitration instead of a master node regulating the bus. Since a CAN network can support a large number of devices, and allows a longer maximum cable length (50 metres before signal degradation forces a slower data rate [9]), CAN is often used for vehicle chassis networks and diagnostics – the OBD-II vehicle diagnostics protocol uses CAN for the communications link, as does SAE J1939.

# Topology

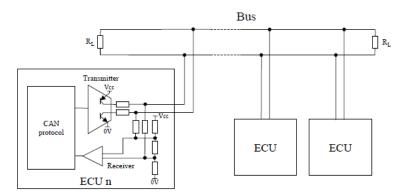

CAN specifies a terminated linear multi–drop passive bus, using differential transmission on a single twisted–pair cable to minimise EMI. The bus lines should be terminated by a  $120\Omega$  resistor. A CAN communications controller may operate on one or more channels simultaneously, each channel being a complete and separate bus. The following diagram (Figure 2.7) is drawn from the ASSC Guide to Digital Interface Standards ([10]), and shows the standard topology and terminal transmitter/receiver configurations as specified in ISO11898 (microcontrollers and devices attached to the bus are called ECUs, Electronic Control Units, in CAN terminology, and indeed often in the field of fieldbuses in general).

#### Addressing

Like many fieldbuses (but unlike most computer networks), CAN is message–addressed rather than node–addressed. That is to say, instead of each node having a unique address and a message being addressed to a particular node, each message has an address (or, more correctly, an identifier) and is broadcast to all nodes. The result is that the message identifier defines the type and thus meaning of the message, and any nodes needing the information contained within it can read it from the bus.

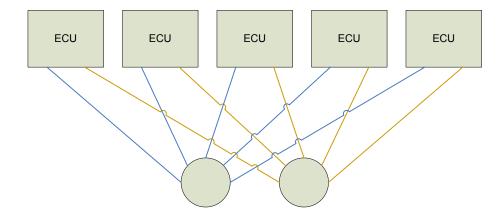

Figure 2.7: ISO11898 CAN Topology (from page 15 of [10])

# Arbitration

As with all multi-master communications networks, arbitration is necessary when two controllers attempt to transmit different messages in the same time quantum. However, unlike in most networks, it is possible to resolve message collisions without corrupting data on the bus. This is achieved by the use of non-destructive bitwise arbitration, in which a logical 0 (defined as "dominant") overrules a logical 1 (defined as "recessive"). In CAN, message identifiers increase in priority as they approach zero (i.e. a message identifier that is numerically lower than another has a higher transmission priority). Since the message identifier is the first field transmitted whenever a message is placed on the bus (see Figure 2.8), the message with the higher priority (and thus the lower-valued identifier) will result in a 0 being placed on the bus before the message with the lower priority. Since all transmitting controllers are required to monitor the content of the bus after each bit transmitted, the controller transmitting the lower priority message will see the 1 it is transmitting overwritten by the 0 from another controller, and cease transmission until the bus is free again. Messages that fail arbitration are queued and retransmitted automatically. By the time the message identifier has been fully transmitted, only one message will remain on the bus, meaning that no corruption will occur (assuming the network was designed well, and each message identifier is transmitted by a maximum of one controller). Since only messages that fail arbitration cease transmission on collision (as opposed to all colliding messages in systems using CSMA-CD such as Ethernet), high-priority messages will tend to reach their destinations with minimal latency. There is, however, the risk that low-priority messages will be permanently held off the bus by higher priority messages (since the identifier of the message is the only attribute upon which arbitration is performed: messages held in the queue do not change priority with time,

resulting in what is essentially a form of scheduling starvation).

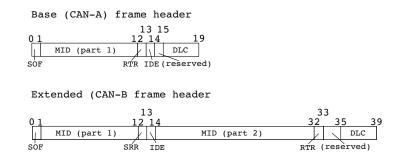

# Variants

A CAN network can use one of two different message formats: the Basic frame format (CAN 2.0A) or the Extended frame format (CAN 2.0B). The Extended format is longer (64-128 bits, as opposed to 44-108 bits in the Basic format), and most of the additional length is in the message identifier; the Basic message identifier is 11 bits in length, while the Extended message identifier is divided into an 11-bit section and an 18-bit section. The formats can be differentiated by inspecting the fourteenth bit of the frame: in a Basic frame, this bit will be dominant (0), and in an Extended frame it will be recessive (1).

The increase in length of a CAN–B identifier (when compared to a CAN–A identifier) has both positive and negative effects on the network. A CAN–A identifier can contain a maximum of 2048 different values, meaning that the network can carry at most 2048 unique commands (with variable data). A CAN–B identifier can hold approximately 536 million different values. If the network has a large number of complex devices attached, or needs to be expandable for future use, 2048 message identifiers may prove insufficient, and a CAN–B based network may be more suitable. However, the use of longer messages without an increase in bus speed will mean that fewer messages can be carried in a given time period, and that bus latency will be increased by a small amount. Additionally, a longer message increases the risk that irregular corruption will damage the message, forcing retransmission.

#### **Frame Formats**