# University of Sussex

#### A University of Sussex DPhil thesis

Available online via Sussex Research Online:

http://sro.sussex.ac.uk/

This thesis is protected by copyright which belongs to the author.

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Please visit Sussex Research Online for more information and further details

# **U**niversity of Sussex

# Development of Microfabricated Ion Traps for Scalable Microwave Quantum Technology

Bjoern Lekitsch

Submitted for the degree of Doctor of Philosophy University of Sussex, Brighton, United Kingdom. November 2013

# Declaration

I hereby declare that this thesis has not been and will not be submitted in whole or in part to another University for the award of any other degree.

Signature:

Bjoern Lekitsch

#### UNIVERSITY OF SUSSEX

BJOERN LEKITSCH, DOCTOR OF PHILOSOPHY

### Development of Microfabricated Ion Traps for Scalable Microwave Quantum Technology

## Abstract

Microfabricated ion traps are an important tool in the development of scalable quantum systems. Tremendous advancements towards an ion quantum computer were made in the past decade and most requirements for a quantum computer have been fulfilled in individual experiments. Incorporating all essential capabilities in a fully scalable system will require the further advancement of established quantum information technologies and development of new trap fabrication techniques.

In my thesis I will discuss the theoretical background and experimental setup required for the operation of ion traps. Measurement of the important ion trap heating rate was performed in the setup and I will discuss the results in more detail.

I will give a review of microfabrication processes used for the fabrication of traps, outlining advantages, disadvantages and issues inherent to the processes. Following the review I will present my work on a concept for a scalable ion trap quantum system based on microwave quantum gates and shuttling through X-junctions.

Many of the required building blocks, including ion trap structures with current-carrying wires intended to create strong magnetic field gradients for microwave gates were investigated further. A novel fabrication process was developed to combine current-carrying wires with advanced multilayered ion trap structures. Several trap designs intended for proof of principle experiments of high fidelity microwave gates, advanced detection techniques and shuttling between electrically disconnected ion traps will be presented. Also the electrode geometry of an optimized X-junction design with strongly suppressed rf barrier height will be presented.

Further, I developed several modifications for the experimental setup to extend the existing capabilities. A plasma source capable of performing in-situ cleans of the trap electrode surfaces, which has been demonstrated to dramatically reduce the heating rate in ion traps, was incorporated. I will also present a vacuum system modification designed to cool ion traps with current-carrying wires and transport the generated heat out of the vacuum system. In addition a novel low-noise, high-speed, multichannel voltage control system was developed by me. The device can be used in future experiments to precisely shuttle ions from one trapping zone to another and also to shuttle ions through ion trap junctions.

Lastly I will outline the process optimization and microfabrication of my ion trap designs. A novel fabrication process which makes use of the extremely high thermal conductivity of diamond substrates and combines it with thick copper tracks embedded in the substrate was developed. Large currents will be passed through the wires creating a strong and controllable magnetic field gradient. Ion trap designs with isolated electrodes connected via buried wires can be placed on top of the current-carrying wires, allowing the most advanced electrode designs to be fabricated with current-carrying wires.

## Acknowledgements

#### **General Acknowledgements**

First and foremost, I wish to express my gratitude to my supervisor, Winfried Hensinger, for giving me the opportunity to work in the Sussex IQT group. His enthusiasm and dedication for our research greatly inspired me. I will never forget the many interesting discussions we had over the years.

I would also like to thank my second supervisor Barry Garraway for all the guidance and help he offered me. Many thanks also go to Micheal Kraft and Ibrahim Sari for supporting my work at the Southampton nanofabrication centre.

I want to thank my colleagues Altaf Nizamani, Robin Sterling, James Siverns, Marcus Hughes, James McLoughlin who setup the experiment before I joined the group and introduced me to the world of ion trapping. Sebastian Weidt, who joined the research group shortly after me, was of great help during our first challenging experiments and has always been extremely helpful. Marcus Hughes, for spending countless hours with me working on the experiment and our microfabrication paper. Kimberly Lake, who was always of great help and who motivated me with her great enthusiasm for physics. Special thanks goes to David Murgia, Simon Webster and Gouri Giri, who provided me with great feedback while working on my thesis. Gouri Giri also assisted me with the development of our voltage control system and was of invaluable help during my time fabricating at the Southampton nanofabrication centre. I would also like to thank the other group members, Darren De Motte, Eamon Standing, Joe Randal and the many undergraduate students who have supported our work on the experiments.

Many thanks also go to Alan Mayers and the other members of the mechanical workshop at Sussex, who gave me good advice whenever designing new parts for the experiment and for their great work when manufacturing these for us. I would also like to thank the staff members of the Southampton nanofabrication centre for the constant support and help with the challenging fabrication processes. A thank you must also go to the group led by Wolfgang Lange and Mathias Keller, who provided us with guidance and shared equipment whenever needed.

I am very greatful to my family for always encouraging, motivating and believing in me. Without their love and support I would have not been able to finish this endevour. My greatest thanks goes to my fiance Nicky Santoyo, for always being there for me and who I will never be able to thank enough for what she did for me over the last two years. Finally, I'd like to thank my close friends: Sebastian Deuser, Frank Klaiber, Felix Waehlisch, Christoff Haller, Marco Stolle, David Christian, Luisa Bohlender, Svenja and Wolfgang Huemmer, who have always been supportive, helpful and provided me with distractions when needed.

#### **Detailed Acknowledgements**

Much of the work presented in this thesis would not have been achievable without the input and help of other members of the group and the Southampton nanofabrication centre. In the following section I will outline their contributions to my thesis chapters.

#### Chapter 3 - Ion Trapping Setup and Initial Experiments

The ion trapping setup was built before I joined the group by Altaf Nizamani, Robin Sterling, James Siverns, Marcus Hughes and James McLoughlin. More specifically, the external cavity diode lasers were constructed by James McLoughlin and Robin Sterling. Laser locking systems were designed and implemented mainly by Robin Sterling and Kimberly Lake with support from Altaf Nizamani, James Siverns, Marcus Hughes and James McLoughlin. The imaging setup was designed and constructed by James Siverns and Marcus Hughes. The first vacuum system was developed and assembled by Altaf Nizamani with the help of James McLoughlin and Robin Sterling. The second vacuum system was developed by Robin Sterling and James Sayers and assembled by Robin Sterling, Sebastian Weidt and Kimberly Lake. The helical resonator was designed and built by James Siverns. The macroscopic blade trap was designed by Robin Sterling and individual parts assembled by Altaf Nizamani, James Siverns, Marcus Hughes, James McLoughlin and Robin Sterling.

Doppler cooling wavelengths were measured by Altaf Nizamani, Robin Sterling, James Siverns, Marcus Hughes, James McLoughlin, myself and Sebastian Weidt.

The theory of the heating measurement was reproduced by myself with some assistance of Altaf Nizamani and James McLoughlin. The measurement was performed by myself, Marcus Hughes, Sebastian Weidt, Altaf Nizamani, James McLoughlin, James Siverns and Robin Sterling.

#### Chapter 4 - Microfabrication Techniques

This chapter is partially based on common work of myself and Marcus Hughes presented in the publication 'Microfabricated Ion Traps'.

#### Chapter 5 - Concept for Scalable Ion Trap Quantum Computing

The concept presented in this chapter was developed by myself. The analysis of the error correction codes is loosely based on prior work of myself, Austin Fowler, Simon Devitt, Altaf Nizamani, Kimberly Lake, Sebastian Weidt and Winfried Hensinger.

#### Chapter 6 - Asymmetric Ion Trap Designs

The two-dimensional array, discussed in this chapter is based on the example case presented in 'Optimisation of two-dimensional ion trap arrays for quantum simulation' and the geometry was optimized by James Siverns, Sebastian Weidt, Kimberly Lake, myself and Marcus Hughes.

#### Chapter 7 - Vacuum Chamber Modifications and Voltage Control System

The development of the voltage control system presented in this chapter was assisted by Gouri Giri.

#### Chapter 8 - Microfabrication of Ion Trap Designs

The fabrication process was developed by myself with help of Ibrahim Sari and Marcus Hughes. Optimization of process steps was performed by myself assisted by Ibrahim Sari, Kian Shen Kiang and Hwanjit Rattanasonti. All of the fabrication steps for the ion trap designs were performed by myself.

# Publications and conference contributions

#### Journal publications

## Versatile ytterbium ion trap experiment for operation of scalable ion-trap chips with motional heating and transition-frequency measurements,

James J. McLoughlin, Altaf H. Nizamani, James D. Siverns, Robin C. Sterling, Marcus D. Hughes, Bjoern Lekitsch, Björn Stein, Seb Weidt, and Winfried K. Hensinger, Phys. Rev. A 83, 013406 (2011).

#### Microfabricated ion traps,

Marcus D. Hughes, Bjoern Lekitsch, Jiddu Broersma and Winfried K. Hensinger, Contemporary Physics 52:6, 505-529 (2011).

#### Optimization of two-dimensional ion trap arrays for quantum simulation,

James D Siverns, Seb Weidt, Kim Lake, Bjoern Lekitsch, Marcus D Hughes and Winfried K Hensinger,

New J. Phys. 14, 085009 (2012).

#### **Conference contributions**

#### Development of ion chips and coherent manipulation of ytterbium ions,

B. Lekitsch, R. C. Sterling, M. D. Hughes, J. D. Siverns, J. J. McLoughlin, S. Weidt, K. Lake, A. H. Nizamani, P. Srinivasan, H. Rattanasonti, J. Maclean, C. Mellor, M. Kraft and W. K. Hensinger

Poster at IonTech 2012, COST-IOTA Workshop 7-9 May 2012, at Siegen, Germany.

# Contents

| Li | st of | Tables | 5                                                                           | xiv |

|----|-------|--------|-----------------------------------------------------------------------------|-----|

| Li | st of | Figur  | es                                                                          | xxi |

| 1  | Intr  | oducti | on                                                                          | 1   |

| 2  | Ion   | Trapp  | ing and the Yb Ion                                                          | 6   |

|    | 2.1   | Electr | ic Fields and Ion Motion in Paul Traps                                      | 6   |

|    |       | 2.1.1  | Ion Motion in the Pseudopotential Approximation                             | 7   |

|    |       | 2.1.2  | Mathieu Equations and Stability Parameters                                  | 11  |

|    |       | 2.1.3  | Analytical Simulations of Electric Fields in Surface Traps $\ldots$ .       | 16  |

|    |       | 2.1.4  | Numerical Simulations of Electric fields                                    | 26  |

|    | 2.2   | Manip  | ulation of Ion Motional States                                              | 29  |

|    |       | 2.2.1  | Doppler Cooling of Motional States                                          | 30  |

|    |       | 2.2.2  | Heating of Motional States                                                  | 32  |

|    | 2.3   | Intern | al States of Yb Ions and Yb Quantum Information Processing $\ldots$ .       | 33  |

|    |       | 2.3.1  | Photoionization of Yb Atoms and Relevant Energy Levels                      | 34  |

|    |       | 2.3.2  | Energy Levels used for Doppler Cooling of Yb Ions                           | 35  |

|    |       | 2.3.3  | Microwave Based Motional State Coupling                                     | 38  |

| 3  | Ion   | Trapp  | ing Setup and Initial Experiments                                           | 40  |

|    | 3.1   | Laser  | Systems and Locking                                                         | 40  |

|    |       | 3.1.1  | External Cavity Diode Lasers (ECDL) and Frequency Doubling Sys-             |     |

|    |       |        | tem $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 41  |

|    |       | 3.1.2  | Laser Locking Schemes                                                       | 44  |

|    |       | 3.1.3  | Optical Table Setup                                                         | 46  |

|    | 3.2   | Imagin | ng Setup                                                                    | 46  |

|    | 3.3   | Vacuu  | m Systems                                                                   | 48  |

|   |     | 3.3.1  | Vacuum Chambers                                                    | 50  |

|---|-----|--------|--------------------------------------------------------------------|-----|

|   | 3.4 | Dc Vo  | ltage Supply, Helical Resonator and Trap Characteristics           | 54  |

|   | 3.5 | Macro  | scopic Ion Trap, Trapping and Initial Experiments                  | 57  |

|   |     | 3.5.1  | Blade Trap                                                         | 57  |

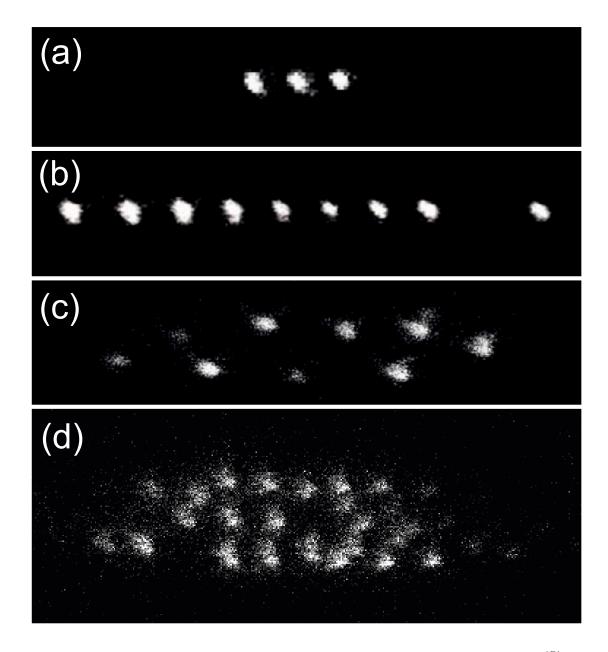

|   |     | 3.5.2  | Initial Trapping                                                   | 60  |

|   |     | 3.5.3  | Measurement of Transition Frequencies of Several Yb Isotopes       | 61  |

|   |     | 3.5.4  | Measuring Secular Frequencies                                      | 61  |

|   | 3.6 | Heatir | ng Rate Measurement and Discussion                                 | 62  |

|   |     | 3.6.1  | Micromotion Compensation                                           | 62  |

|   |     | 3.6.2  | Experimental Recording of Fluorescence Curves                      | 63  |

|   |     | 3.6.3  | Micromotion caused by RF Phase Mismatch                            | 68  |

| 4 | Mic | rofabr | ication Techniques                                                 | 71  |

|   | 4.1 | Voltag | ge Breakdown and Surface Flashover                                 | 72  |

|   | 4.2 | RF El  | ectrode Capacitance, Power Dissipation and Loss Tangent $\ldots$ . | 74  |

|   |     | 4.2.1  | Capacitance Calculation of RF Electrodes                           | 74  |

|   |     | 4.2.2  | Inductance Calculation of RF Electrodes                            | 75  |

|   |     | 4.2.3  | Resistance of RF Electrode                                         | 76  |

|   |     | 4.2.4  | Loss Tangent of the Dielectric Layer                               | 76  |

|   |     | 4.2.5  | Power Dissipation in Ion Trap Structures                           | 77  |

|   | 4.3 | Extrin | sic Micromotion and Motional Heating                               | 78  |

|   |     | 4.3.1  | Micromotion                                                        | 79  |

|   |     | 4.3.2  | Anomalous heating                                                  | 81  |

|   | 4.4 | Micro  | fabrication Technologies                                           | 83  |

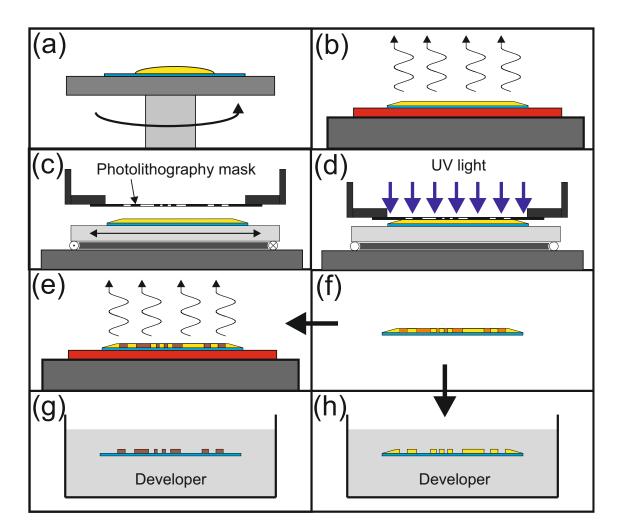

|   |     | 4.4.1  | Lithography                                                        | 84  |

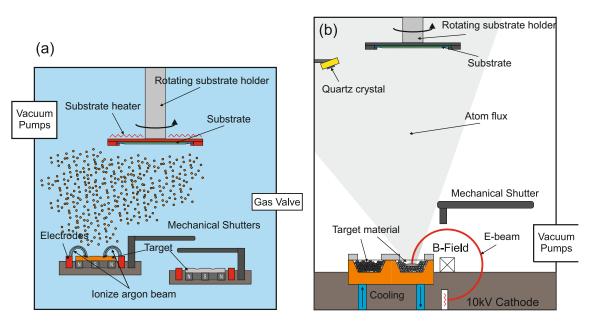

|   |     | 4.4.2  | Deposition                                                         | 87  |

|   |     | 4.4.3  | Etching                                                            | 89  |

|   | 4.5 | Fabric | eation Processes                                                   | 92  |

|   |     | 4.5.1  | Printed Circuit Board (PCB)                                        | 93  |

|   |     | 4.5.2  | Conductive Structures on Substrate (CSS)                           | 95  |

|   |     | 4.5.3  | Patterned Silicon on Insulator Layers (SOI)                        | 98  |

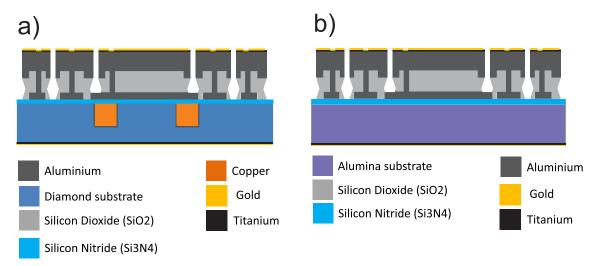

|   |     | 4.5.4  | Conductive Structures on Insulator with Buried Wires (CSW)         | 100 |

|   |     | 4.5.5  | Conductive Structures on Insulator with Ground Layer (CSL)         | 101 |

|   |     | 4.5.6  | Optimized Structures for Large Scale Ion Traps with Magnetic Field |     |

|   |     |        | Gradients(OLM)                                                     | 103 |

| 5 | Cor | ncept f     | or Scalable Ion Trap Quantum Computing                            | 105 |

|---|-----|-------------|-------------------------------------------------------------------|-----|

|   | 5.1 | Error       | Correction Scheme                                                 | 107 |

|   | 5.2 | Scalab      | ble Ion Trap Architecture and Entanglement Schemes                | 107 |

|   | 5.3 | Juncti      | on Design and Fabrication                                         | 109 |

|   | 5.4 | Entan       | glement Zone                                                      | 111 |

|   | 5.5 | Power       | Dissipation and Cooling                                           | 113 |

|   | 5.6 | State       | Detection and Loading Zone                                        | 114 |

|   | 5.7 | Vacuu       | m System                                                          | 115 |

|   | 5.8 | Conclu      | usion                                                             | 117 |

| 6 | Asy | <b>mmet</b> | ric Ion Trap Designs                                              | 118 |

|   | 6.1 | Trap 1      | Design, Electric Field Modelling and Mask design                  | 119 |

|   |     | 6.1.1       | AutoCAD Model                                                     | 119 |

|   |     | 6.1.2       | BEMSolver                                                         | 120 |

|   |     | 6.1.3       | Calculation of Pseudopotential and Trap Parameters                | 120 |

|   | 6.2 | Proces      | $\operatorname{ss}\operatorname{Limitations}$                     | 121 |

|   | 6.3 | X-Jun       | ction Trap Design                                                 | 122 |

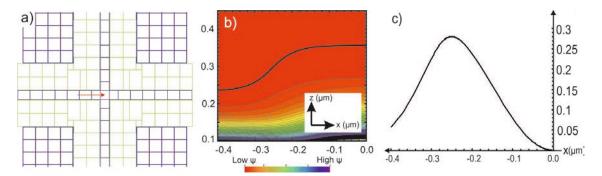

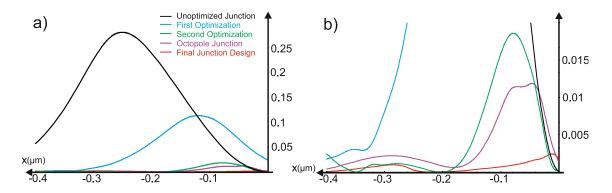

|   |     | 6.3.1       | First Optimization of X-Junction                                  | 124 |

|   |     | 6.3.2       | Further Optimization of X-Junction                                | 125 |

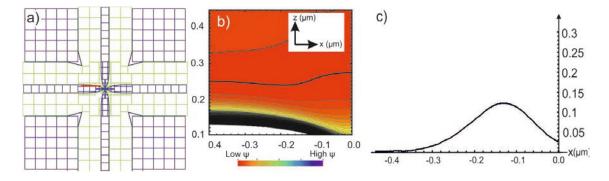

|   |     | 6.3.3       | Octupole X-Junction                                               | 125 |

|   |     | 6.3.4       | Final X-Junction Design                                           | 125 |

|   |     | 6.3.5       | Ion Trap Design and Electrical Characteristics                    | 127 |

|   |     | 6.3.6       | Conclusion                                                        | 128 |

|   | 6.4 | Curren      | nt-Carrying Wire Structures for Asymmetric Traps                  | 133 |

|   |     | 6.4.1       | Challenges                                                        | 133 |

|   |     | 6.4.2       | Wire Material Choice                                              | 134 |

|   |     | 6.4.3       | Power Dissipation of Wire Structures                              | 134 |

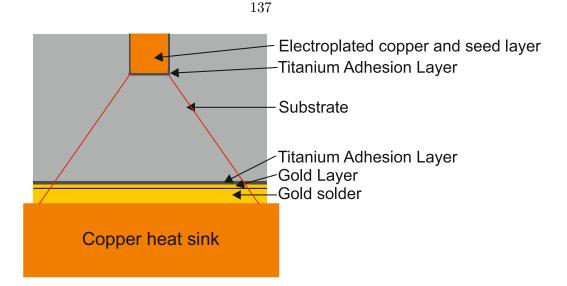

|   |     | 6.4.4       | Thermal Gradient Between Wire Structures and Heat Sink $\ldots$ . | 136 |

|   |     | 6.4.5       | Maximum Current Density                                           | 138 |

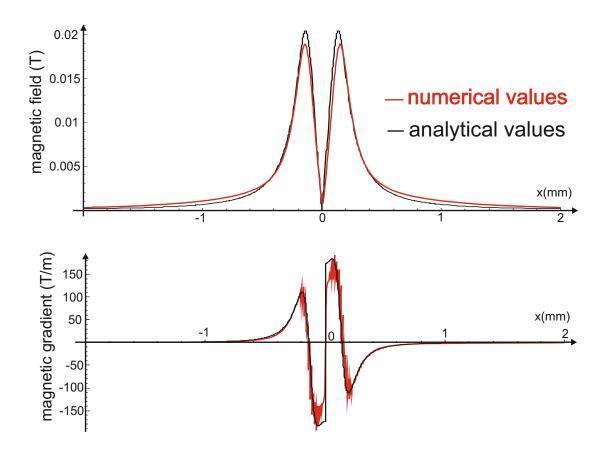

|   |     | 6.4.6       | Static Magnetic Field Strength and Gradient                       | 138 |

|   |     | 6.4.7       | Conclusion                                                        | 140 |

|   | 6.5 | Trap l      | Design for Current-Carrying Wire Structures                       | 140 |

|   | 6.6 | Asym        | metric Traps with Loading/Detection Zones and Disconnected RF     |     |

|   |     | Rails       |                                                                   | 142 |

|   |     | 6.6.1       | Loading and Detection Slot Designs                                | 142 |

|   |     | 6.6.2  | Asymmetric Ion Trap with Separated RF Rails         | . 144 |

|---|-----|--------|-----------------------------------------------------|-------|

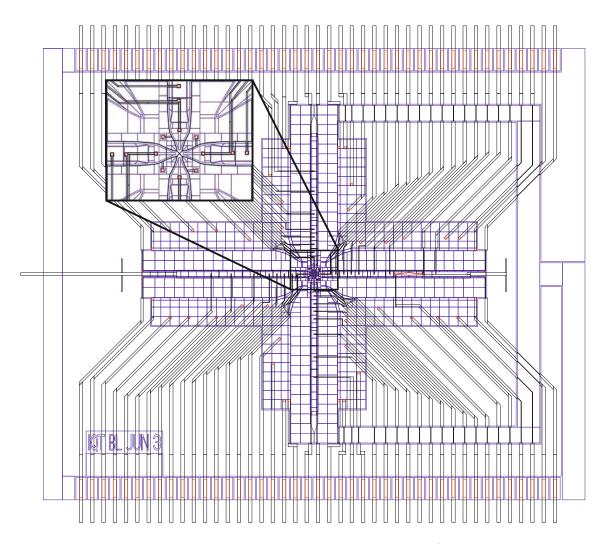

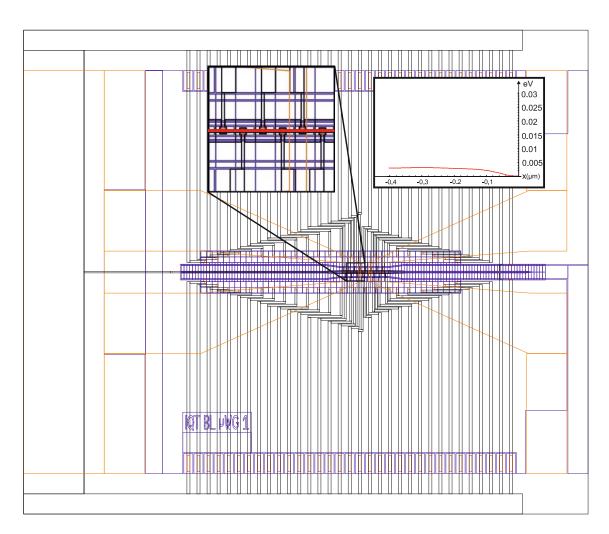

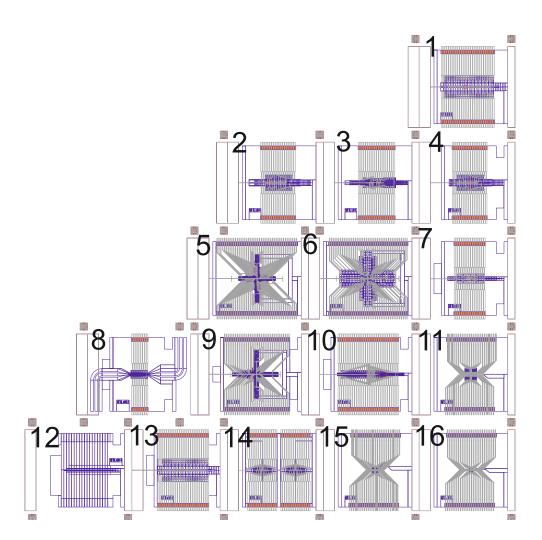

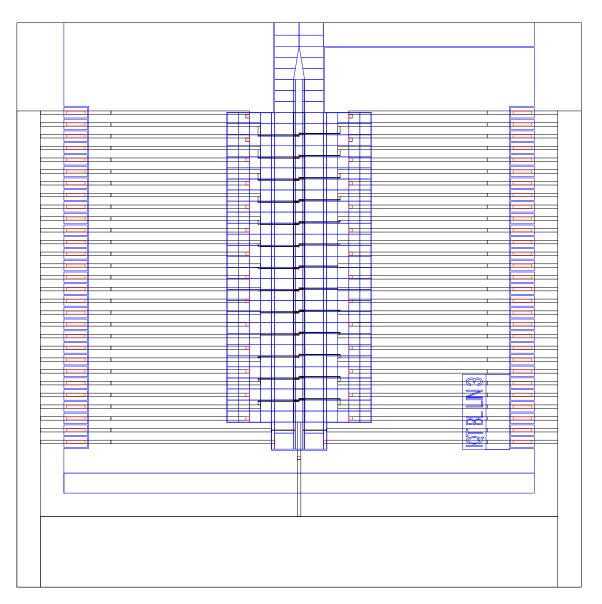

|   | 6.7 | Comp   | olete Mask Layout                                   | . 146 |

| 7 | Vac | uum (  | Chamber Modifications and Voltage Control System    | 151   |

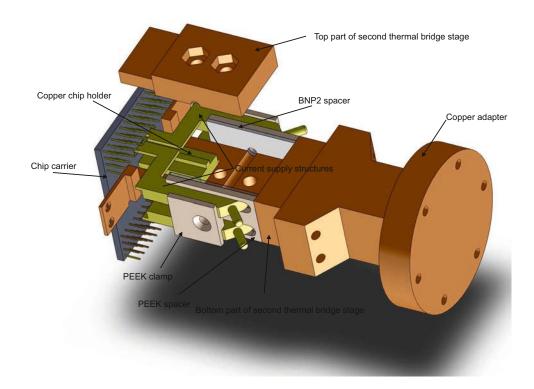

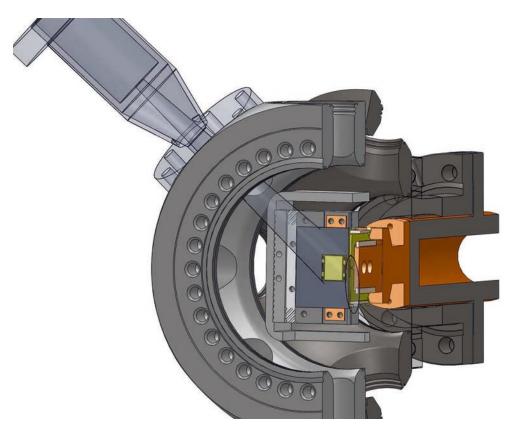

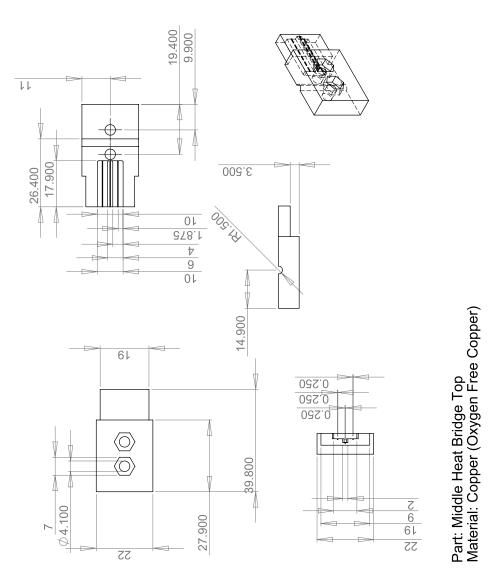

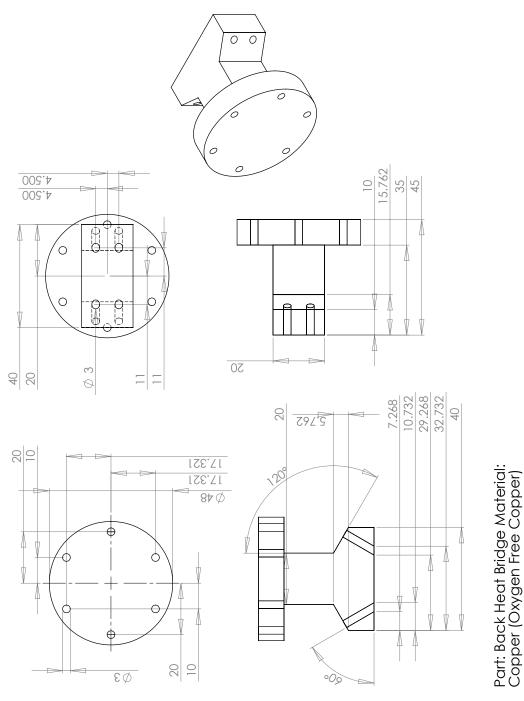

|   | 7.1 | Therr  | nal Transport System                                | . 151 |

|   |     | 7.1.1  | Chip Holder                                         | . 152 |

|   |     | 7.1.2  | Thermal Bridge and Current Supply Structures        | . 153 |

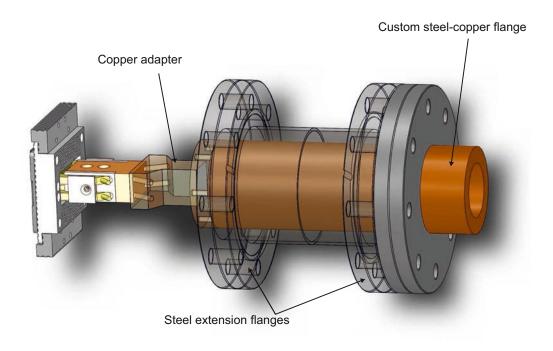

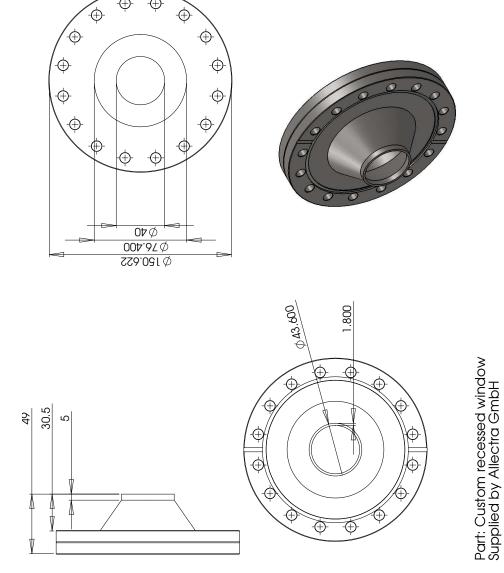

|   |     | 7.1.3  | Copper Adapters and custom Steel-Copper Flange      | . 155 |

|   |     | 7.1.4  | Conclusion                                          | . 158 |

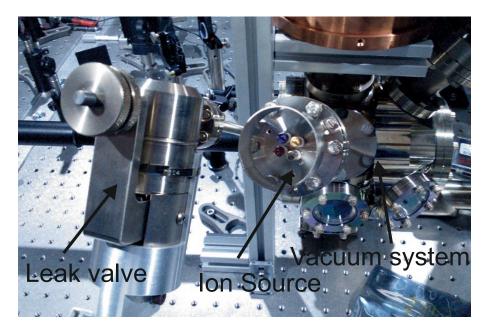

|   | 7.2 | Plasm  | ha Source for <i>in situ</i> Ion Trap Cleaning      | . 158 |

|   |     | 7.2.1  | Ion Source                                          | . 159 |

|   |     | 7.2.2  | Custom Flange                                       | . 159 |

|   |     | 7.2.3  | Operation                                           | . 160 |

|   | 7.3 | Volta  | ge Control System                                   | . 160 |

|   |     | 7.3.1  | Digital-to-Analogue Converters                      | . 161 |

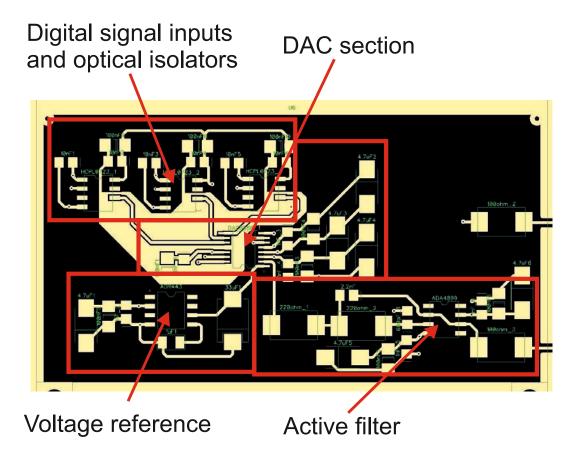

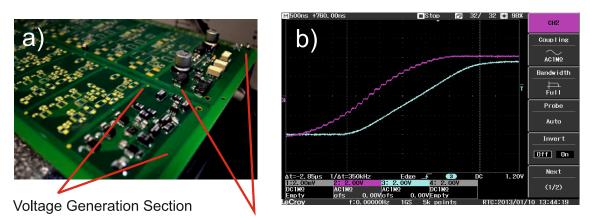

|   |     | 7.3.2  | Voltage Generation and Active Filtering             | . 163 |

|   |     | 7.3.3  | Printed Circuit Boards                              | . 165 |

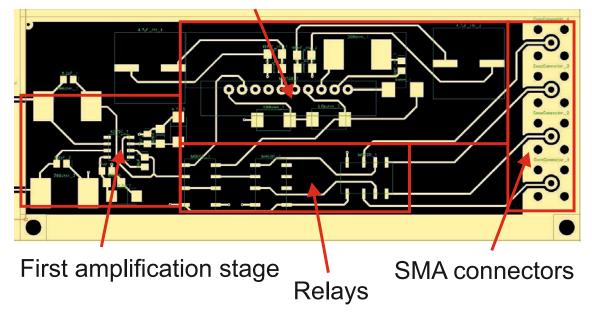

|   |     | 7.3.4  | Voltage Amplification                               | . 166 |

|   |     | 7.3.5  | Voltage Supplies                                    | . 167 |

|   |     | 7.3.6  | Testing of the Voltage Control System               | . 167 |

|   |     | 7.3.7  | Conclusion                                          | . 168 |

| 8 | Mic | rofabr | rication of Ion Traps                               | 170   |

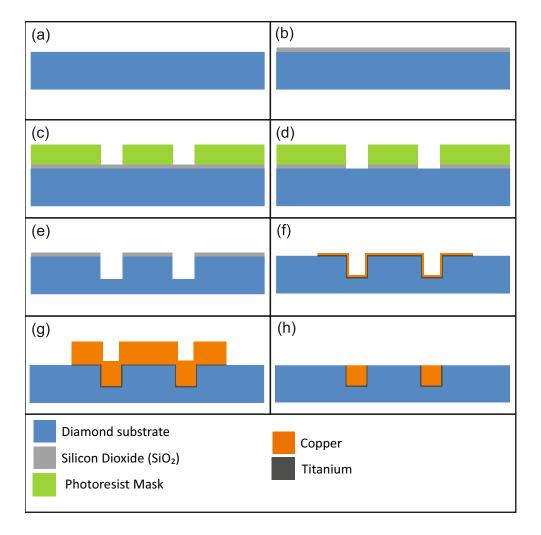

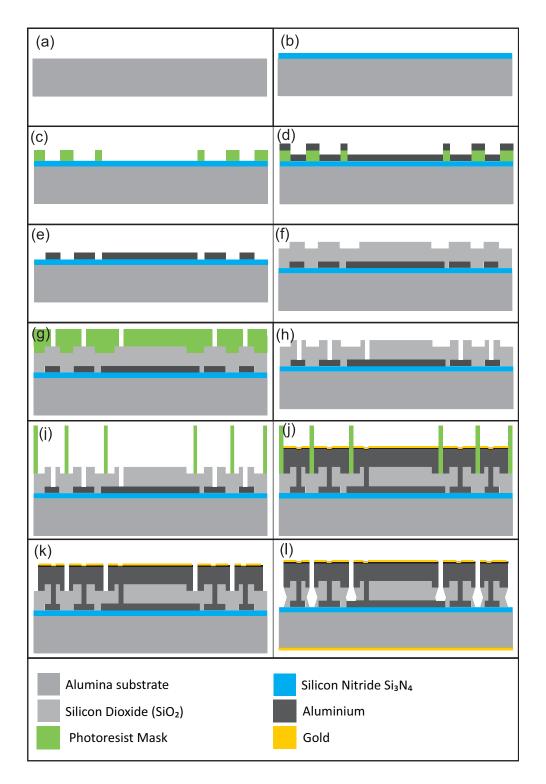

|   | 8.1 | Proce  | ss Overview                                         | . 170 |

|   |     | 8.1.1  | Current-Carrying Wire Structures                    | . 170 |

|   |     | 8.1.2  | Ion Trap Structures                                 | . 172 |

|   | 8.2 | Fabrie | cation of CCW Structures                            | . 172 |

|   |     | 8.2.1  | Substrate Preparation                               | . 174 |

|   |     | 8.2.2  | Substrate Cleaning                                  | . 174 |

|   |     | 8.2.3  | Deposition of $SiO_2$ Hard Mask                     | . 176 |

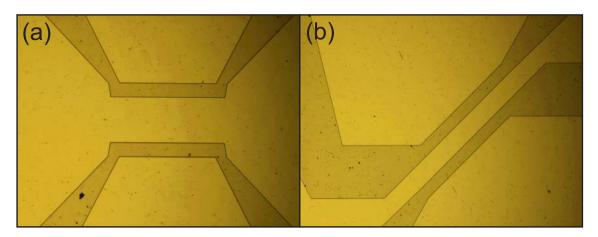

|   |     | 8.2.4  | Photoresist Mask to Structure the Hard Mask         | . 177 |

|   |     | 8.2.5  | Etching of $SiO_2$ Hard Mask and Diamond Substrates | . 179 |

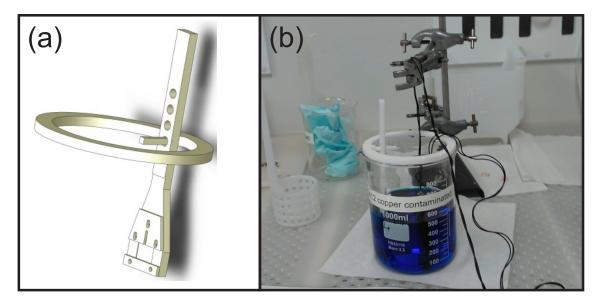

|   |     | 8.2.6  | Metallization of Current-Carrying Wires             | . 181 |

|   | 8.3 | Fabrie | cation of Ion Trap Structures                       | . 183 |

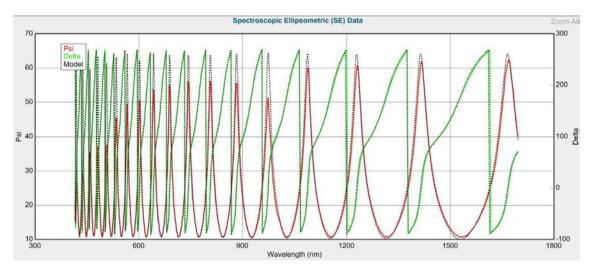

|   |     | 8.3.1  | High Breakdown Voltage Insulating layer             | . 184 |

|    |       | 8.3.2   | Buried Wire Steps                                            | .84 |

|----|-------|---------|--------------------------------------------------------------|-----|

|    |       | 8.3.3   | Deposition and Structuring of Insulating Layer               | 86  |

|    |       | 8.3.4   | Lithography and Deposition of Trap Electrodes                | 87  |

|    | 8.4   | Conclu  | usion and outlook                                            | .90 |

| 9  | Con   | clusio  | n and Outlook 1                                              | 91  |

| Bi | bliog | graphy  | 1                                                            | 93  |

| Α  | The   | oretica | al Description of Ion Fluorescence During Doppler Recooling2 | 14  |

| В  | Det   | ailed N | Aicrofabrication Processes 2                                 | 17  |

|    | B.1   | Plasma  | a Etch and Ash Process Details                               | 217 |

|    | B.2   | Plasma  | a Deposition (PECVD) Process Details                         | 220 |

|    | B.3   | Resist  | Coating Process Details                                      | 221 |

|    | B.4   | Physic  | al Vapour Deposition (PVD) Process Details                   | 223 |

| С  | Hea   | tbridg  | e Designs 2                                                  | 26  |

|    | C.1   | SolidW  | Vorks Drawings                                               | 226 |

| D  | Mas   | skLayo  | ut 2                                                         | 39  |

|    | D.1   | Individ | lual Mask Designs                                            | 239 |

# List of Tables

| 3.1 | Table with all relevant helical resonator parameters used for described ex-   |    |

|-----|-------------------------------------------------------------------------------|----|

|     | periments                                                                     | 56 |

| 3.2 | Table with dc and rf voltages applied to the electrodes for initial trapping  |    |

|     | and experiments.                                                              | 59 |

| 3.3 | Doppler cooling transition wavelengths measured for a variety of Yb isotopes. | 61 |

| B.1 | AZ nLOF 2070 4 $\mu$ m spin profile                                           | 21 |

| B.2 | AZ nLOF 2070 $4\mu$ m spin profile                                            | 22 |

| B.3 | AZ nLOF 2070 $4\mu$ m spin profile                                            | 22 |

# List of Figures

| 1.1  | Illustration showing a two-dimensional trapping array made up of X-junctions                          |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | forming a two-dimensional grid                                                                        | 5  |

| 2.1  | Hyperbolic shaped electrodes and resulting two-dimensional saddle potential.                          | 7  |

| 2.2  | Time averaged trapping potential generated by an alternating potential                                |    |

|      | applied to the hyperbolic electrodes                                                                  | 7  |

| 2.3  | Parallel plates with applied potential $\phi$ and corresponding $E$ field                             | 9  |

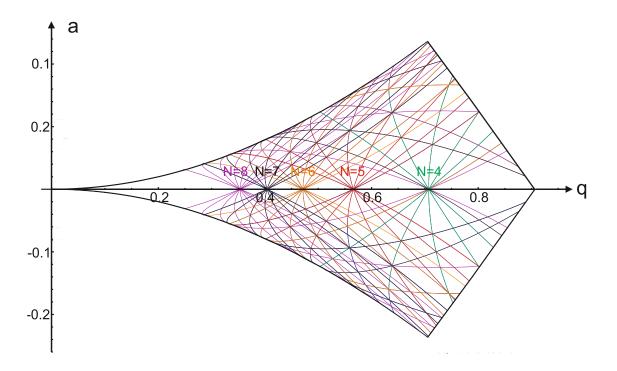

| 2.4  | Stability diagram showing the regions of stable solutions.                                            | 14 |

| 2.5  | Ion motion in one and two dimensions versus time                                                      | 15 |

| 2.6  | Rectangular shaped electrode with corresponding coordinates                                           | 17 |

| 2.7  | The two-dimensional pseudopotential created by a 5 wire geometry ion trap.                            | 20 |

| 2.8  | Rotated pseudopotentials created by asymmetric electrodes and four dc                                 |    |

|      | rotation rails.                                                                                       | 22 |

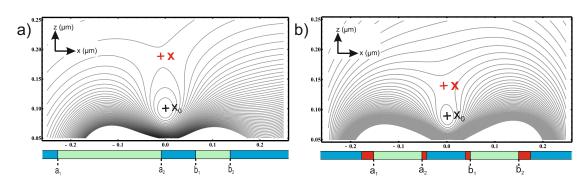

| 2.9  | Modified Stability diagram including instability caused by perturbations to                           |    |

|      | the quadrupole field.                                                                                 | 24 |

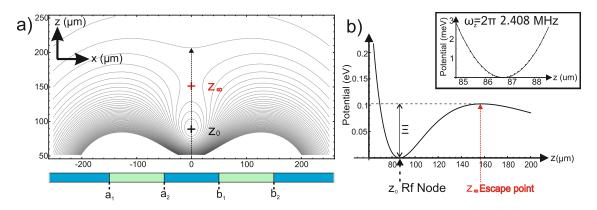

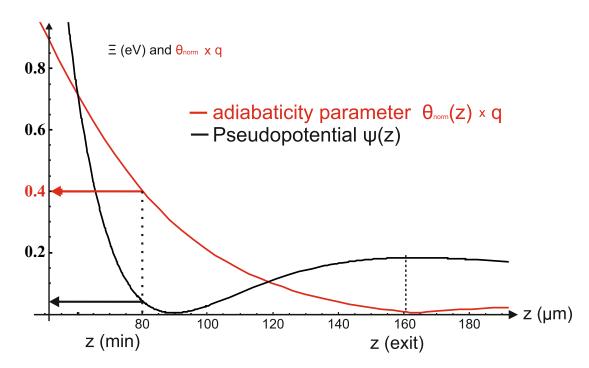

| 2.10 | Adiabaticity parameter and pseudopotential plotted for an example case                                | 25 |

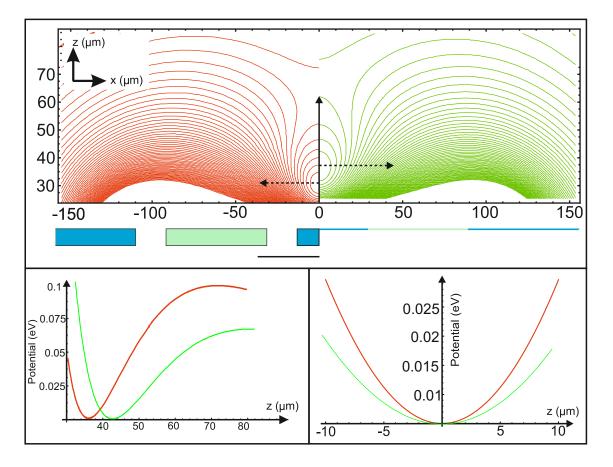

| 2.11 | Comparison of the pseudopotential determined using the analytic gapless                               |    |

|      | plane approximation and a numerical method                                                            | 27 |

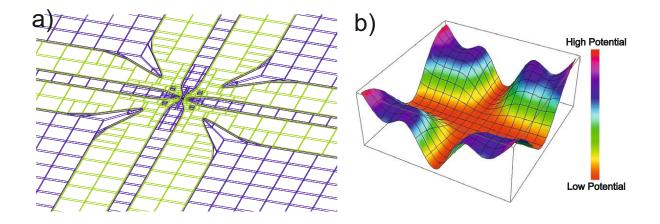

| 2.12 | Junction structure designed in AutoCAD and corresponding 3D plot show-                                |    |

|      | ing the pseudopotential.                                                                              | 29 |

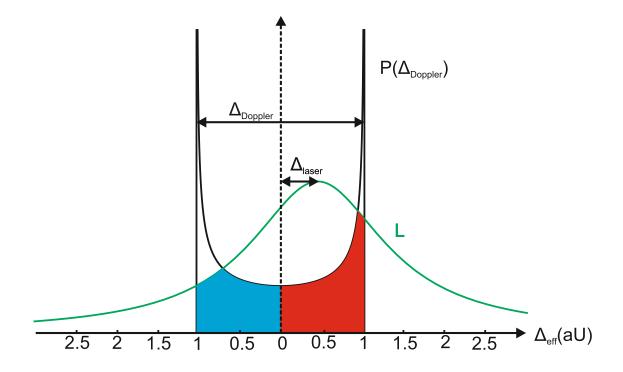

| 2.13 | Doppler shift probability $P_{Doppler}$ and Lorentzian transition line width L.                       | 31 |

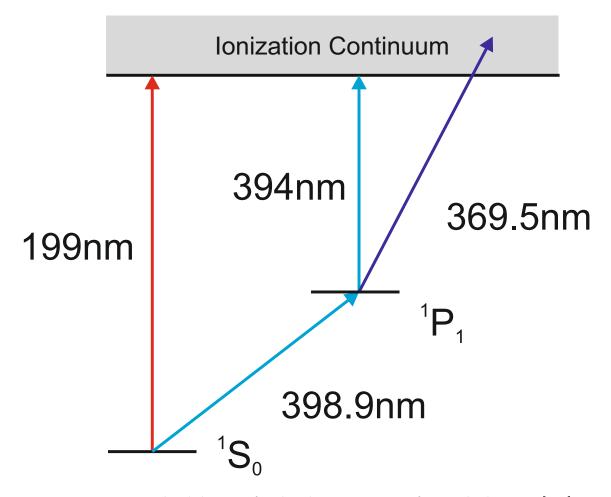

| 2.14 | Energy level diagram for the photo-ionization of neutral Yb atoms                                     | 34 |

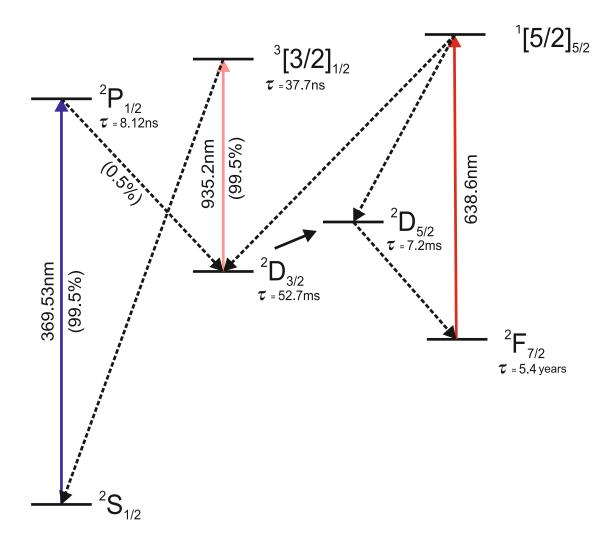

| 2.15 | Relevant internal states of $^{174}$ Yb <sup>+</sup> Doppler cooling                                  | 36 |

| 2.16 | Internal states for <sup>171</sup> Yb <sup>+</sup> Doppler cooling including the hyperfine splitting. | 37 |

| 2.17 | The gradient and therefore position dependent Zeeman shifts are illustrated                           |    |

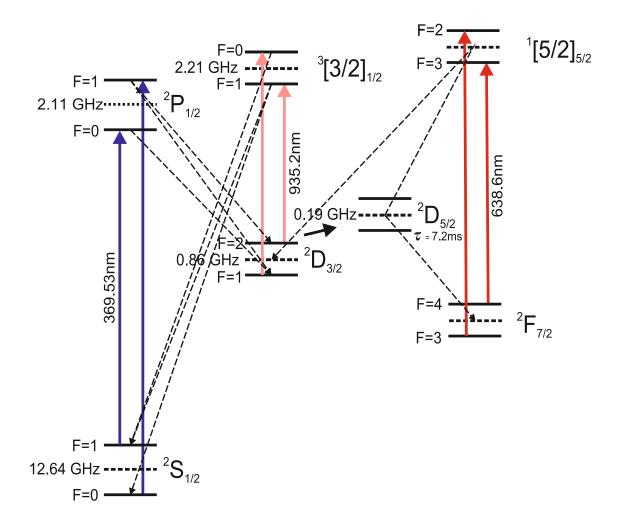

|      | for the magnetic field sensitive state $F = 1, \ldots, \ldots, \ldots, \ldots$                        | 38 |

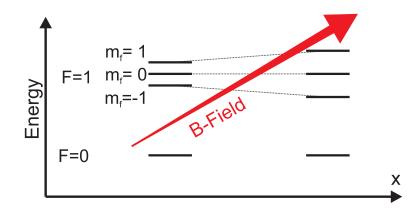

| 3.1  | Bandgap and horizontal structure of a laser diode.                                                | 41 |

|------|---------------------------------------------------------------------------------------------------|----|

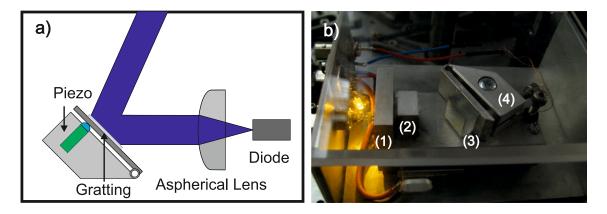

| 3.2  | Schematic and picture of the external cavity diode laser setup, showing the                       |    |

|      | laser diode, aspheric lens and grating.                                                           | 42 |

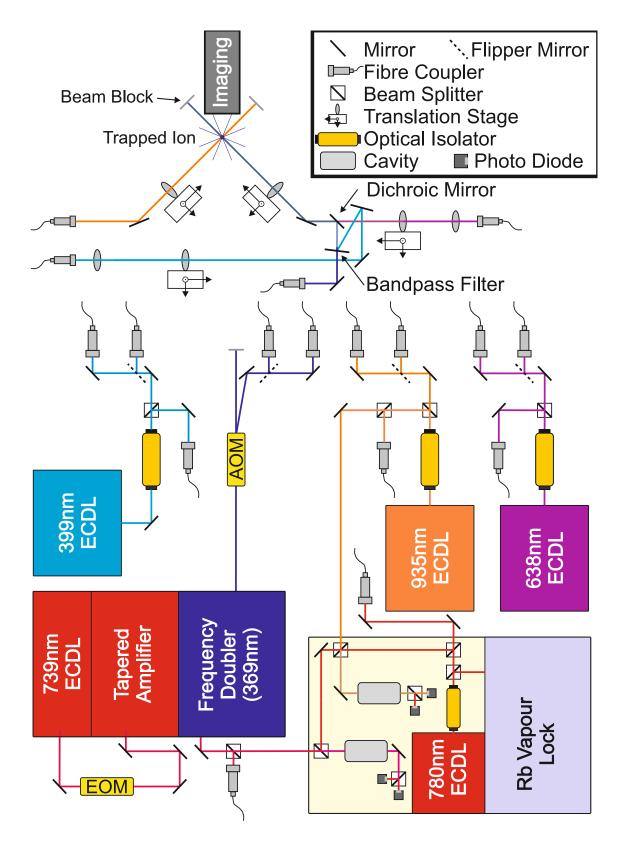

| 3.3  | Overview of the laser and locking setup used for the experiments discussed                        |    |

|      | in this chapter.                                                                                  | 47 |

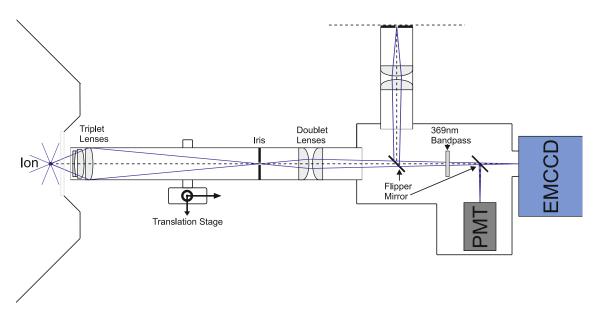

| 3.4  | Schematic of the imaging setup for two vacuum systems                                             | 48 |

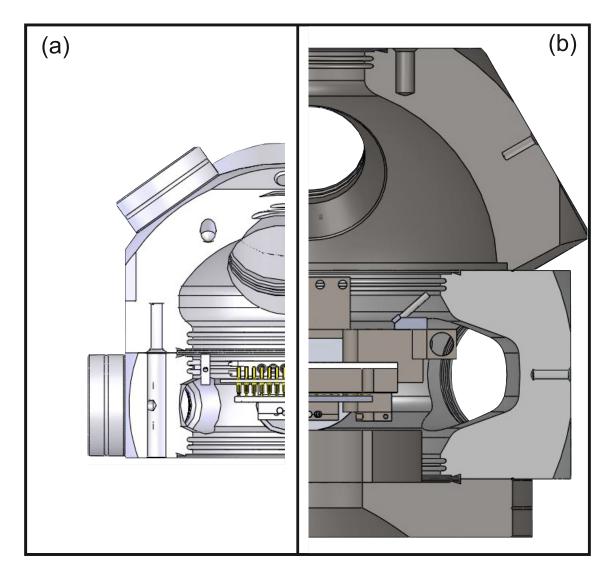

| 3.5  | SolidWorks illustrations with cuts through half the chambers of both vac-                         |    |

|      | uum systems.                                                                                      | 51 |

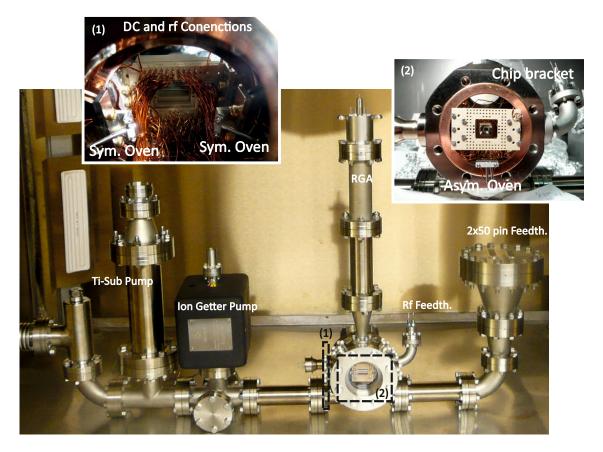

| 3.6  | Picture of the assembled vacuum system one inside the oven chamber used                           |    |

|      | for baking                                                                                        | 53 |

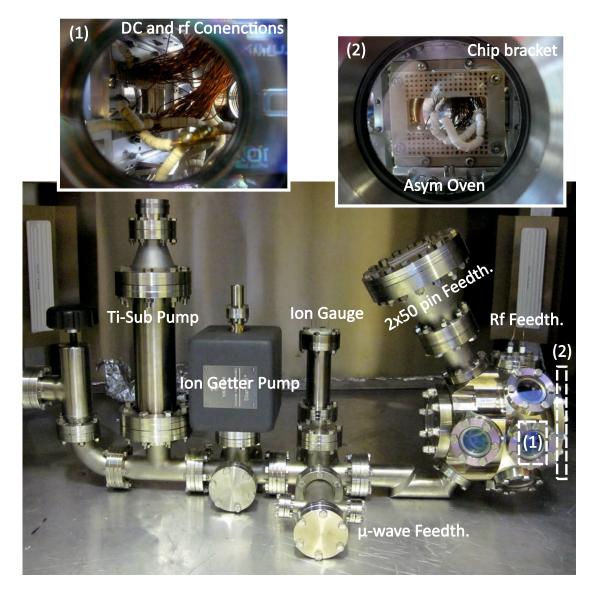

| 3.7  | Assembled vacuum system two inside the same baking oven as system one.                            | 54 |

| 3.8  | Pictures of parts and the entire helical resonator and a schematic illustrating                   |    |

|      | the relevant parameters                                                                           | 55 |

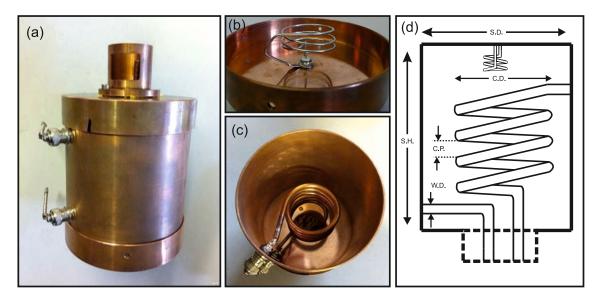

| 3.9  | Cross-section and three-dimensional drawing of the blade trap. $\ldots$ .                         | 58 |

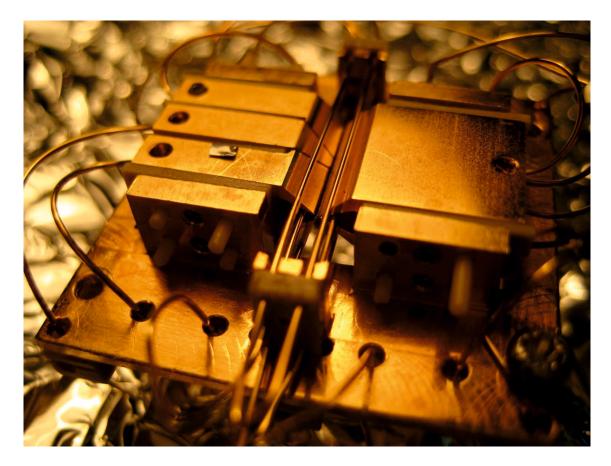

| 3.10 | Picture of the assembled blade trap with wiring and mounting plate                                | 58 |

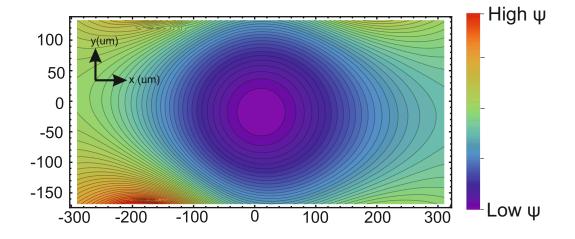

| 3.11 | Pseudopotential simulations of the blade trap showing the potential in <b>x</b>                   |    |

|      | and y axis at $z_0$                                                                               | 59 |

| 3.12 | Pictures showing various trapped $Yb^+$ ions                                                      | 60 |

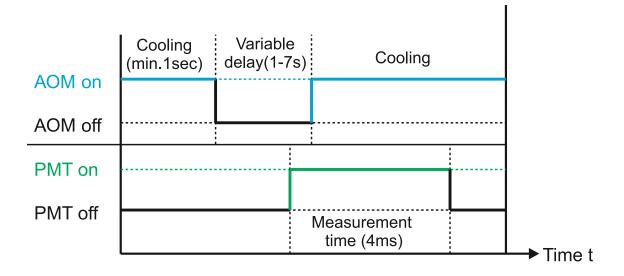

| 3.13 | Time schematic illustrating the timings used to measure the gain in mo-                           |    |

|      | tional quanta of the ion after a certain delay.                                                   | 64 |

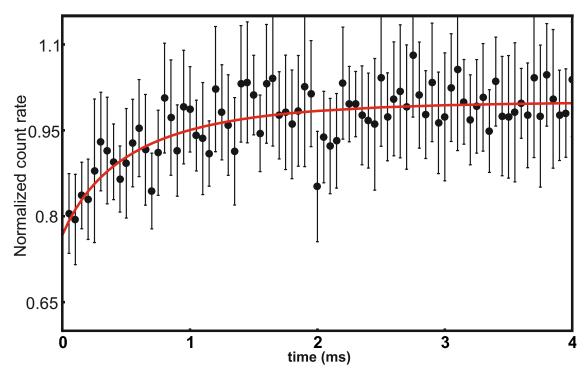

| 3.14 | Normalized count rates summed up from 500 runs for $\omega_z = 178(1)$ kHz with                   |    |

|      | a delay time of 5 sec.                                                                            | 65 |

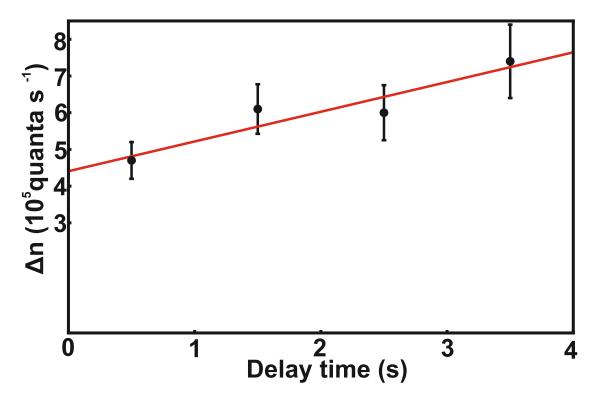

| 3.15 | The gained motional quanta for $\omega_z$ = $2\pi$ $\times$ 178(1)kHz after a 1,3,5,7 sec         |    |

|      | delay time is plotted and fitted with a linear fit                                                | 66 |

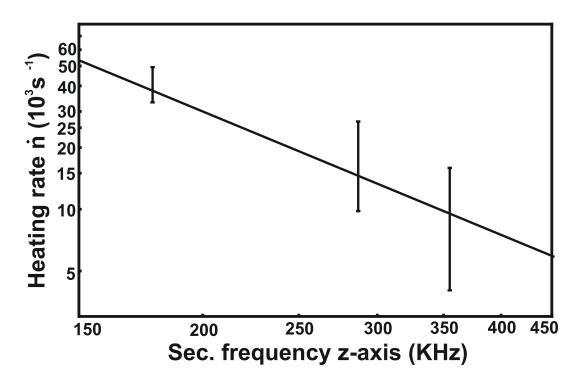

| 3.16 | Plotting the heating rates for different secular frequencies $\omega_z = 2\pi \times 178(1)$ kHz, | ,  |

|      | $\omega_z = 2\pi \times 287(1)$ kHz and $\omega_z = 2\pi \times 355(1)$ kHz vs $\omega$ .         | 67 |

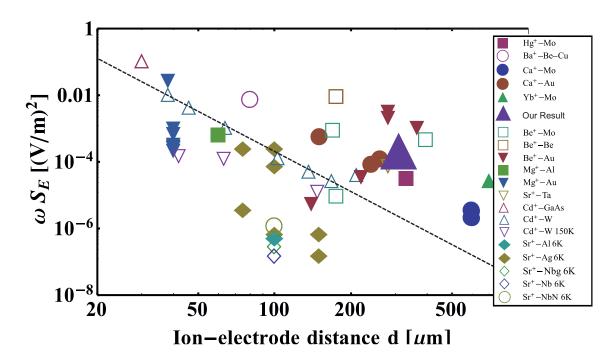

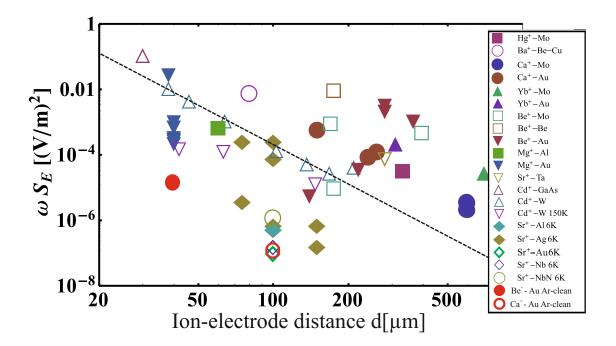

| 3.17 | Heating rate vs ion electrode distance for different ion trap experiments                         |    |

|      | marked according to ion species.                                                                  | 67 |

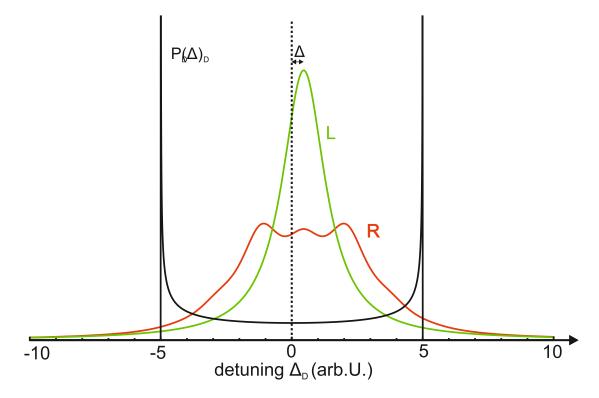

| 3.18 | Power broadened transition linewidth L and micromotion modulated tran-                            |    |

|      | sition linewidth R are plotted with the probability density P. $\ldots$ .                         | 70 |

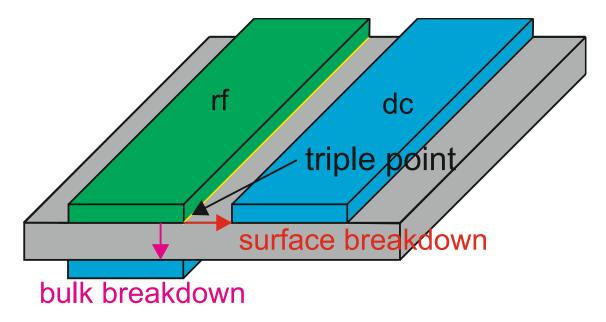

| 4.1  | Schematic illustrating the paths for bulk and surface breakdown.                                  | 73 |

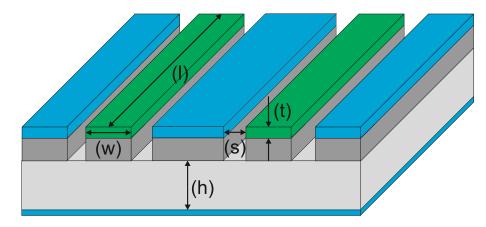

| 4.2  | Example of an ion trap structure used to illustrate the calculations of $C, R$ ,                  |    |

|      |                                                                                                   | 74 |

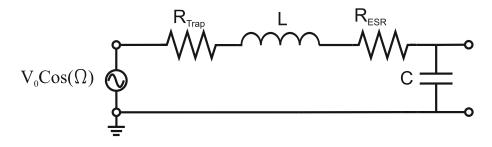

| 4.3  | Rf electrode model showing $R_{\text{Trap}}$ , $C$ , $L$ and $R_{\text{ESR}}$                     |    |

|      |                                                                                                   |    |

| 4.4  | Schematic showing different causes of extrinsic micromotion                  | 80  |

|------|------------------------------------------------------------------------------|-----|

| 4.5  | Comparison of published measurements of motional heating                     | 83  |

| 4.6  | Schematic of the photolithography process.                                   | 86  |

| 4.7  | Schematics showing a sputter deposition tool and an E-beam deposition tool.  | 88  |

| 4.8  | Schematics showing a PECVD reactor chamber and a simple copper elec-         |     |

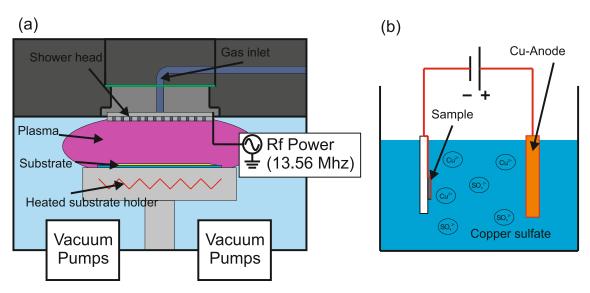

|      | troplating setup.                                                            | 90  |

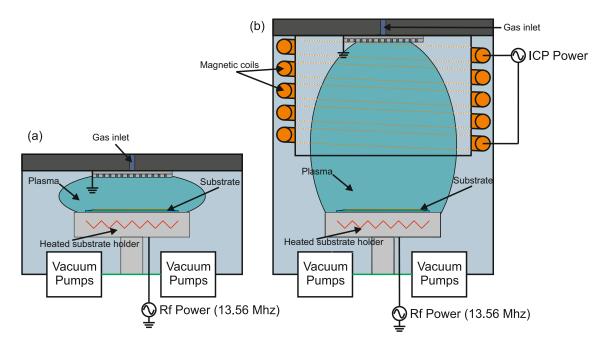

| 4.9  | Schematic showing an RIE chamber and an ICP tool.                            | 91  |

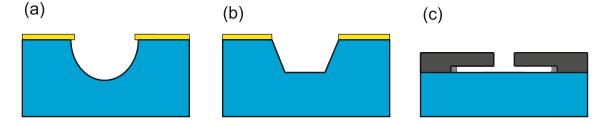

| 4.10 | Schematic showing different wet etch profiles.                               | 92  |

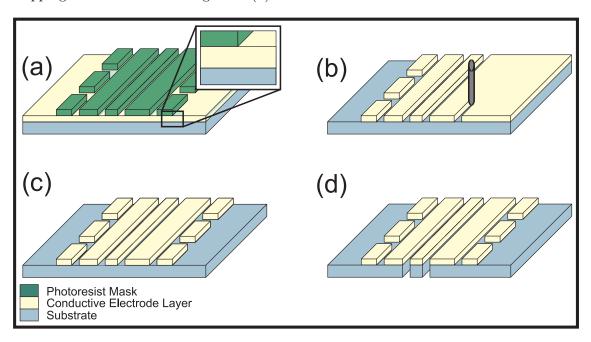

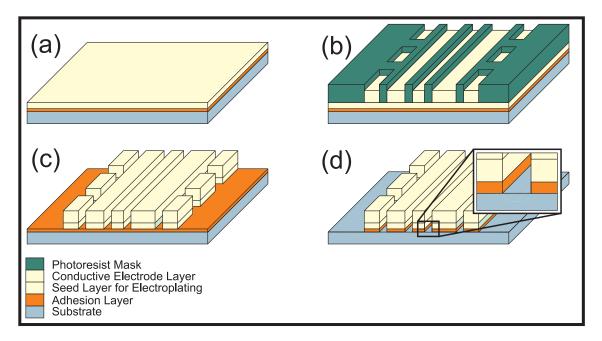

| 4.11 | Overview of several PCB fabrication processes.                               | 94  |

| 4.12 | Fabrication sequence of the standard "Conductive Structures on Substrate"    |     |

|      | process                                                                      | 96  |

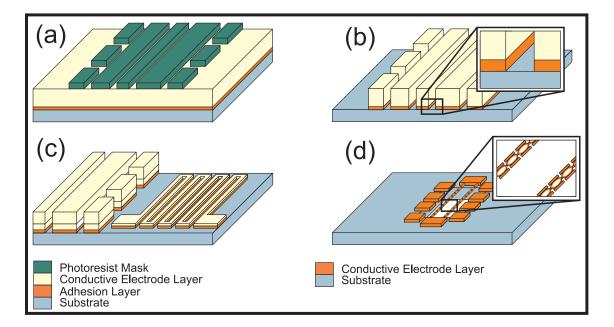

| 4.13 | Different variations of the standard CSS process are shown.                  | 97  |

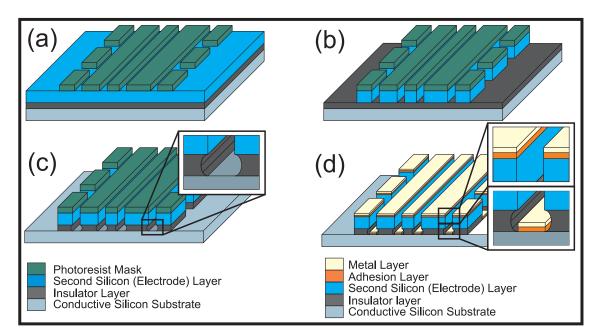

| 4.14 | Fabrication sequence of the SOI process.                                     | 100 |

| 4.15 | Process sequence for the buried wire process.                                | 101 |

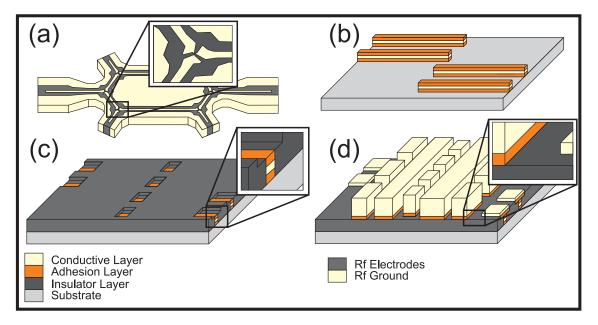

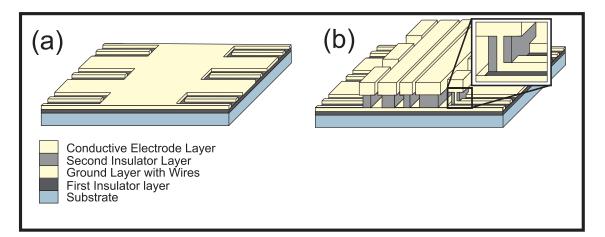

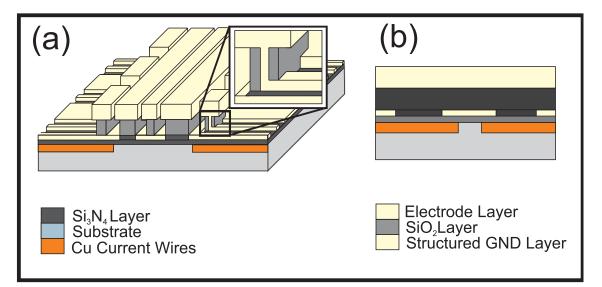

| 4.16 | Two variations of the CSL process sequence.                                  | 102 |

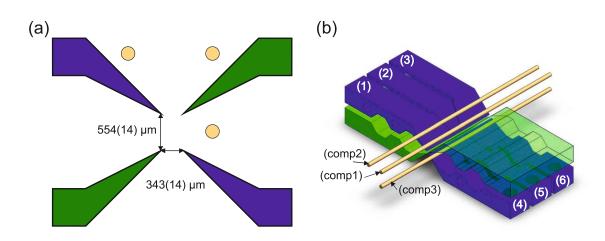

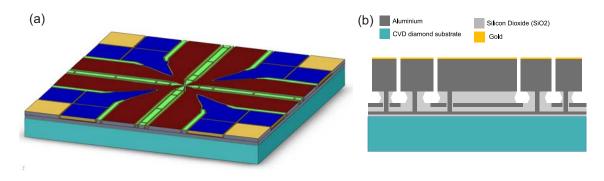

| 4.17 | The OLM process makes use of the high thermal conductivity of CVD            |     |

|      | diamond substrate in which current carrying wires are embedded               | 103 |

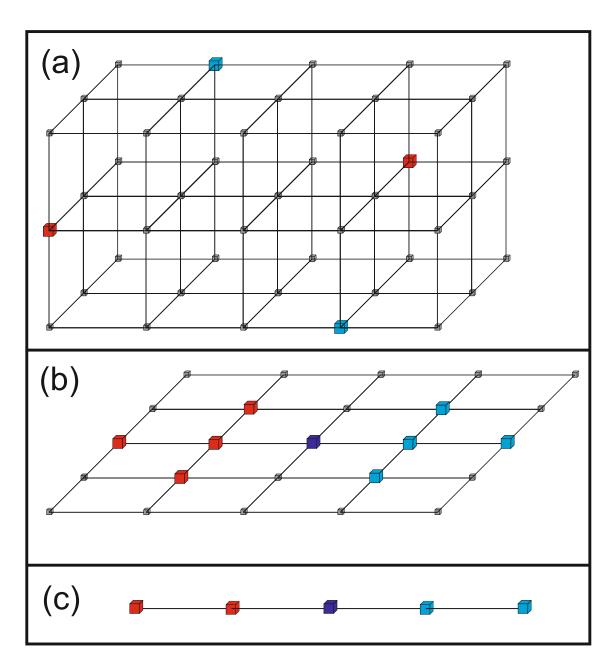

| 5.1  | Schematic showing the required interactions for different error correction   |     |

| 5.1  | codes                                                                        | 106 |

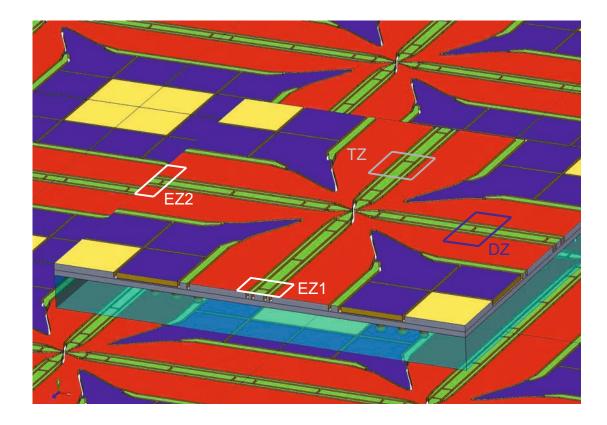

| 5.2  | Illustration showing an individual junction section as part of a large two-  | 100 |

| 0.2  |                                                                              | 108 |

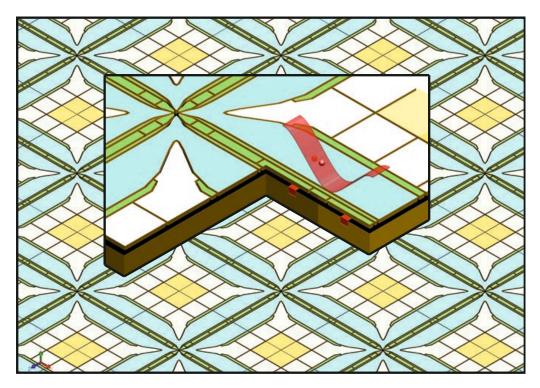

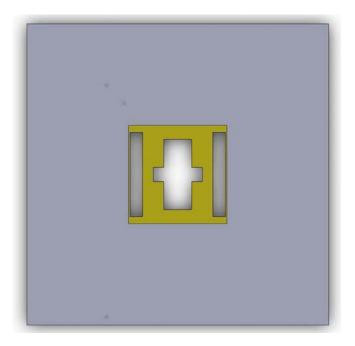

| 5.3  | Optimized junction electrodes geometry on top of a diamond substrate and     | 100 |

| 0.0  | corresponding layer structure                                                | 109 |

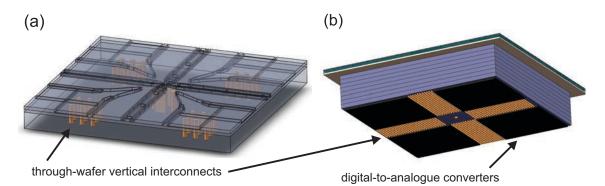

| 5.4  | Illustration showing the wiring of the chips and a backside view of an array | 200 |

| 0.1  | of 6x6 junctions including DACs                                              | 110 |

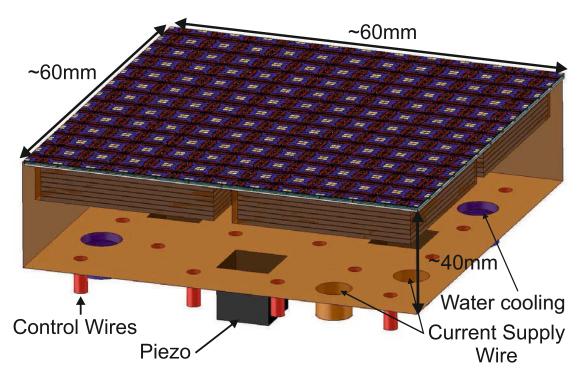

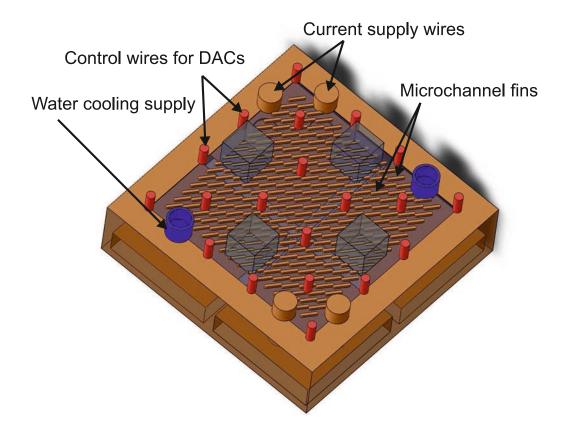

| 5.5  | A large 12x12 array of junction sections including wafer stacked DACs is     |     |

| 0.0  | shown, embedded in a copper heat management socket.                          | 111 |

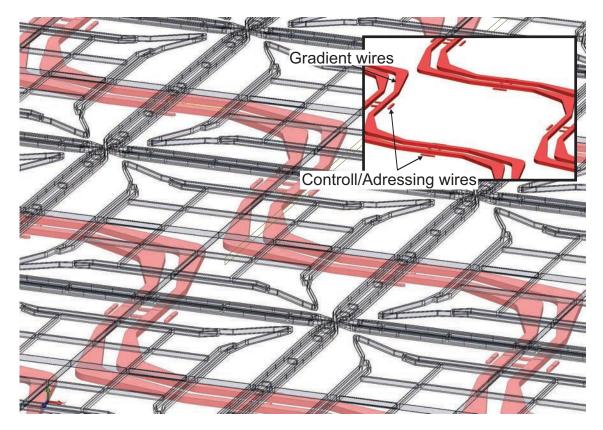

| 5.6  | illustration of the gradient wires placed underneath the trap structure 1    |     |

| 5.7  | Picture of the copper heat sink with microchannel cooler.                    |     |

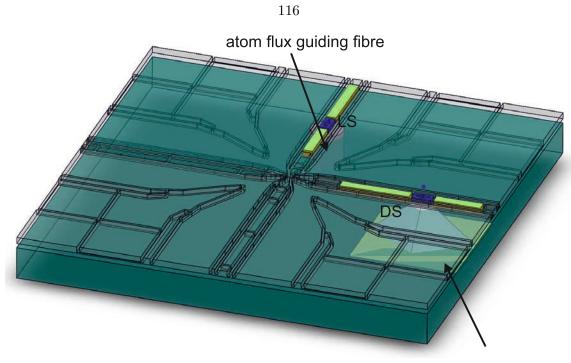

| 5.8  | Showing an optimized X-junction with a loading (LS) and a detection slot     |     |

|      | (DS)                                                                         | 116 |

| 5.9  | Schematic of one octagonal UHV chamber connected to a second chamber         | -   |

| -    | via an air lock.                                                             | 116 |

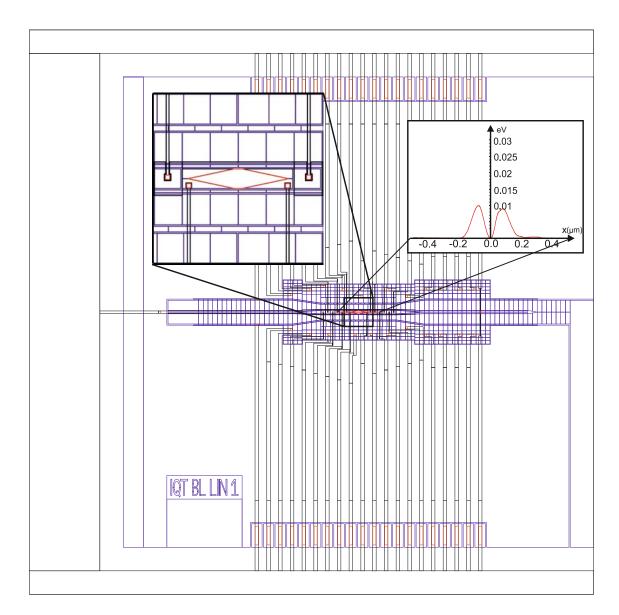

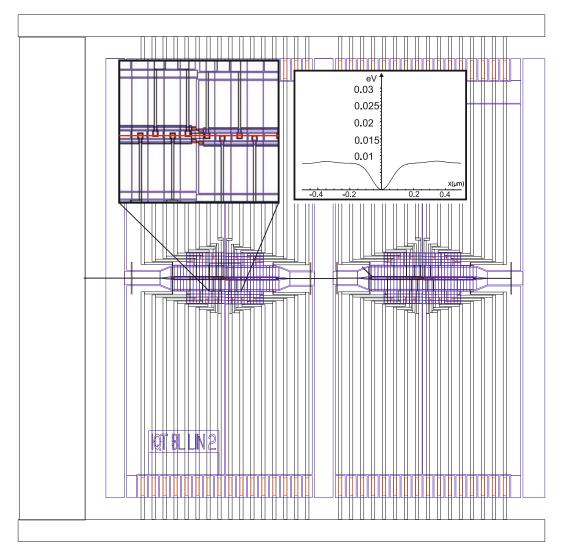

| 6.1  | Showing a design created in AutoCAD and the same design imported by           |       |

|------|-------------------------------------------------------------------------------|-------|

|      | the BEMSolver.                                                                | 119   |

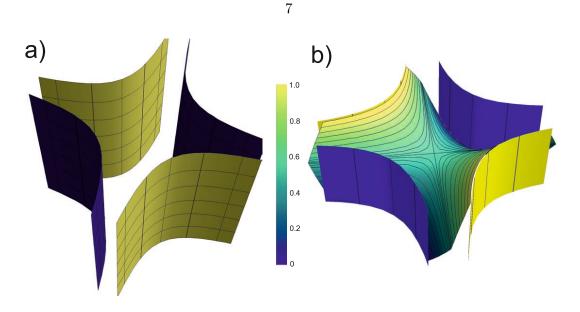

| 6.2  | Pseudopotential of simulated electrode geometries visualized using Mathe-     |       |

|      | matica.                                                                       | 120   |

| 6.3  | Vertical and layer structure of an ion trap fabricated on a diamond substrate |       |

|      | with current-carrying wires and buried wires to connected isolated electrodes | s.122 |

| 6.4  | Unoptimized junction section, corresponding ion height and barrier height     |       |

|      | graphs                                                                        | 124   |

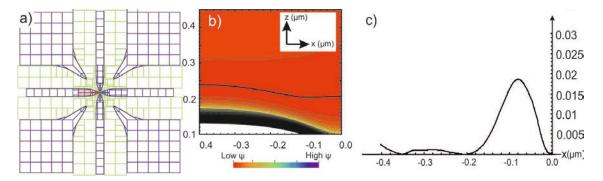

| 6.5  | First optimization of junction section, corresponding ion height and barrier  |       |

|      | height graphs.                                                                | 124   |

| 6.6  | Refined X-junction geometry, corresponding ion height and barrier height      |       |

|      | graphs                                                                        | 125   |

| 6.7  | Octupole X-junction design, corresponding ion height and barrier height       |       |

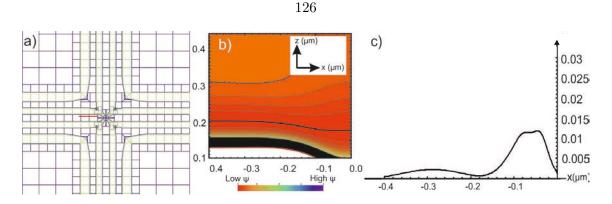

|      | graphs                                                                        | 126   |

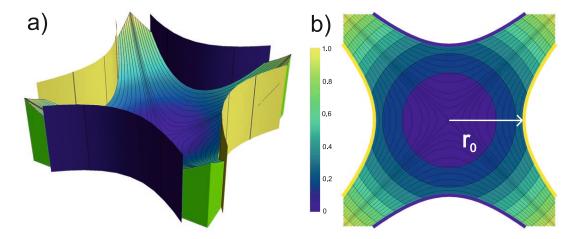

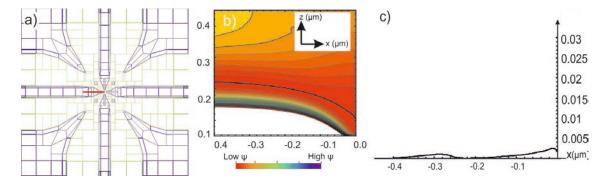

| 6.8  | Final design of the optimized X-junction geometry, corresponding ion height   |       |

|      | and barrier height graphs.                                                    | 126   |

| 6.9  | Comparison of normalized barrier heights for all presented designs            | 127   |

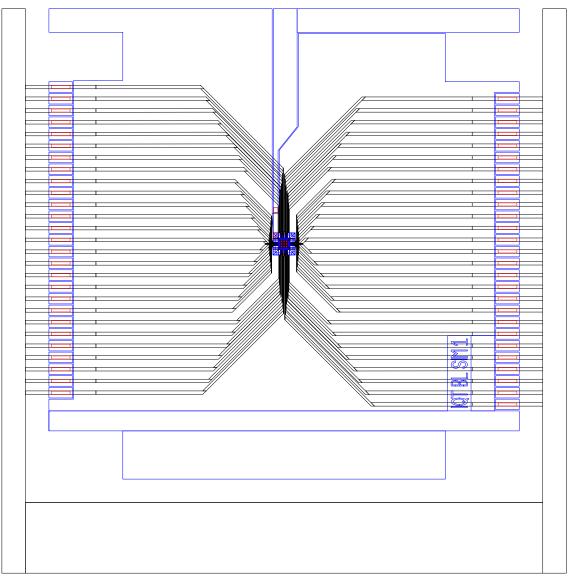

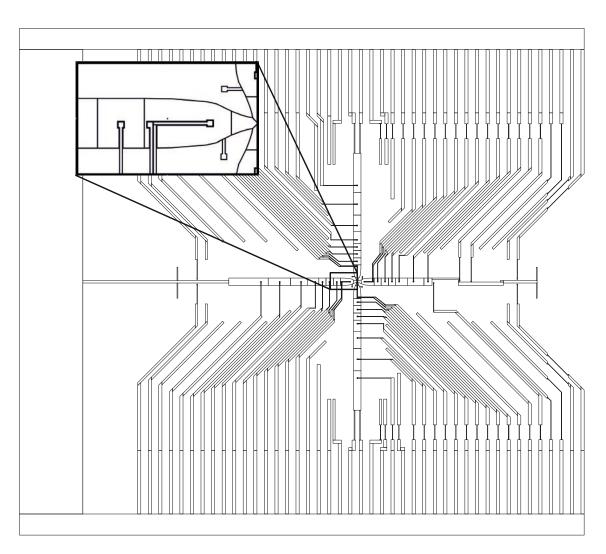

| 6.10 | Shows the electrode layer of the X-junction chip design.                      | 129   |

| 6.11 | Shows the buried wire layer including the structured ground plate. $\ldots$ . | 130   |

| 6.12 | Shows the vertical interconnect access layer design                           | 131   |

| 6.13 | Shows all three layers overlapped with each other.                            | 132   |

| 6.14 | Shows the current-carrying wire structure                                     | 135   |

| 6.15 | Illustration of the layer structure of the ion trap involved in the transport |       |

|      | of heat generated in current-carrying wires.                                  | 137   |

| 6.16 | Comparison between gradients simulated by CST Studio suit FEM tool and        |       |

|      | analytically calculated for the wire structure presented.                     | 139   |

| 6.17 | Linear ion trap section with narrowed rf electrodes to reduce the capacitance |       |

|      | when current-carrying wires are placed underneath                             | 141   |

| 6.18 | Linear ion trap with detection slot for backside detection of scattered light |       |

|      | from a trapped ion                                                            | 143   |

| 6.19 | Showing the two ion trap designs intended for investigations of shuttling     |       |

|      | through separated and shifted rf rails.                                       | 145   |

| 6.20 | Picture of all ion trap designs placed in a quarter of the 6" diameter write  |       |

|      | field mask                                                                    | 150   |

xviii

| 7.1  | Picture showing the modified chip carrier, slots are laser cut into the central |

|------|---------------------------------------------------------------------------------|

|      | cavity plate                                                                    |

| 7.2  | Gold plated copper chip holder and chip carrier with laser cut slots 153        |

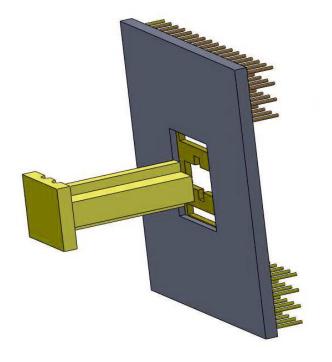

| 7.3  | Showing the chip carrier and copper chip holder attached to the thermal         |

|      | bridge                                                                          |

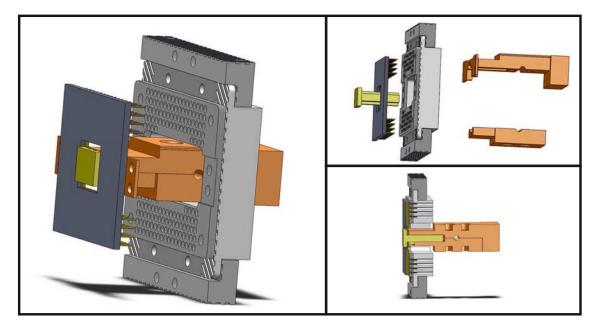

| 7.4  | Assembled thermal bridge, including chip carrier, chip holder, both parts       |

|      | of the thermal bridge, current supply structure and corresponding mounts        |

|      | and copper adapter                                                              |

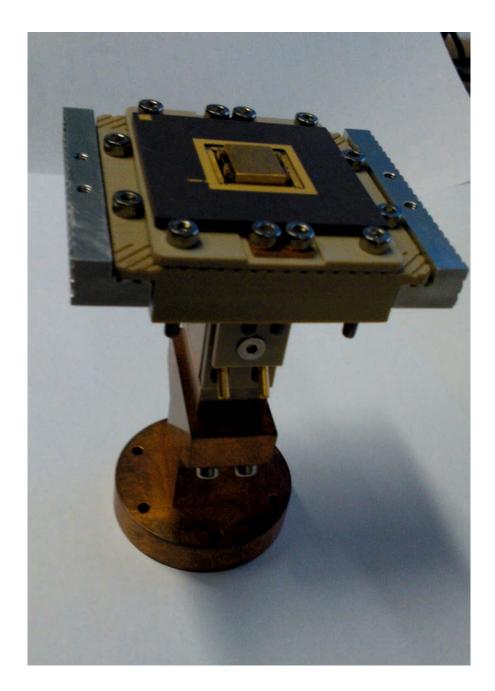

| 7.5  | Picture of the assembled thermal bridge, chip bracket and copper adapter 156    |

| 7.6  | Showing the entire thermal bridge, copper adapter, steel-copper flange and      |

|      | steel extension flanges                                                         |

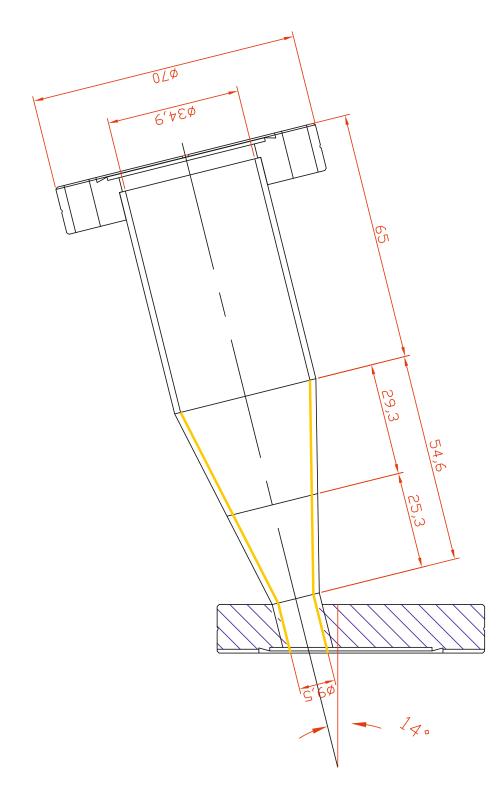

| 7.7  | Cutaway view of the vacuum system, custom flange, ion beam (transparent         |

|      | conus) and thermal transport system                                             |

| 7.8  | Picture of ion source and leak valve attached to a vacuum system 161            |

| 7.9  | Custom designed flange used to attach the ion source to the vacuum system. 162  |

| 7.10 | Voltage generation and active filter section for one channel                    |

| 7.11 | Amplification section of one channel including relays and SMA connectors. 166   |

| 7.12 | Picture of the PCB with components assembled for one channel and Wave-          |

|      | form generated by the system                                                    |

| 8.1  | Schematic of the process used to fabricate current-carrying wires               |

| 8.2  | Fabrication of ion trap structures is illustrated for alumina based traps 173   |

| 8.3  | Graph showing the measured Psi (red) and Delta (green) parameter vs             |

|      | wavelength and a model of the layer structure fitted to the data (dashed) 177   |

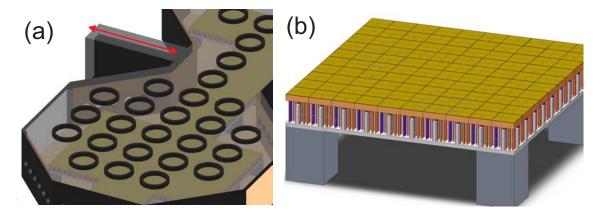

| 8.4  | Pictures of trench patterns in a photoresist mask for a linear section (a)      |

|      | and a two-dimensional array (b)                                                 |

| 8.5  | (a) Illustration showing the teffon sample holder and (b) picture of the        |

|      | assembled plating setup                                                         |

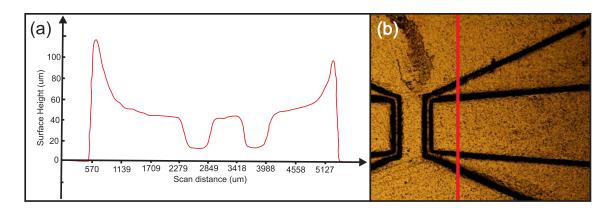

| 8.6  | Height profile of electroplated diamond sample vs scan distance and picture     |

|      | of the corresponding copper trenches                                            |

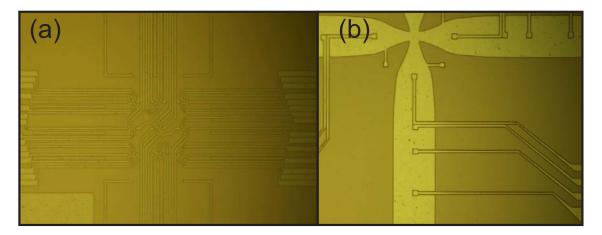

| 8.7  | Pictures of developed resist structures for a two-dimensional array (a) and     |

|      | an X-junction in (b)                                                            |

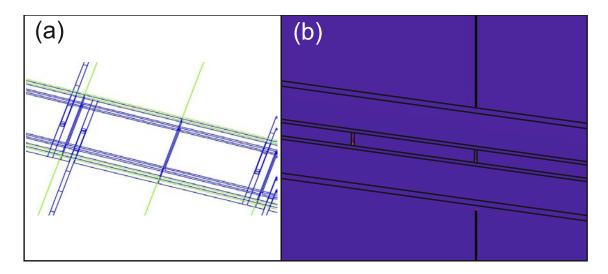

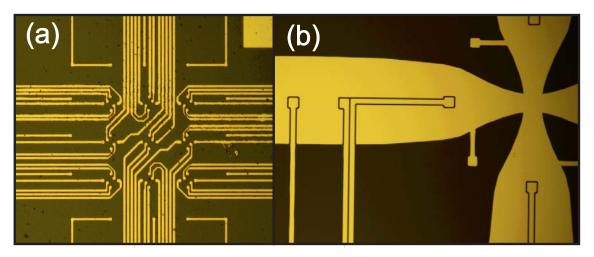

| 8.8  | Pictures showing Al buried wires of a 2D trapping array (a) and X-junction      |

|      | design (b)                                                                      |

| 8.9  | Showing the alignment of the VIA resist etch mask with the buried wires 187     |

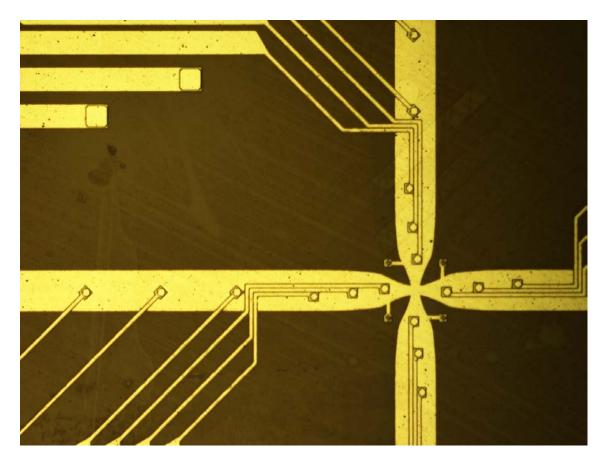

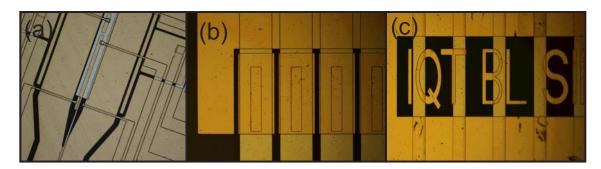

| <ul><li>8.10 Electrode Layer structures after lift-off process, showing (a) linear section,</li><li>(b) bond pads and (c) labelling of the trap</li></ul> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

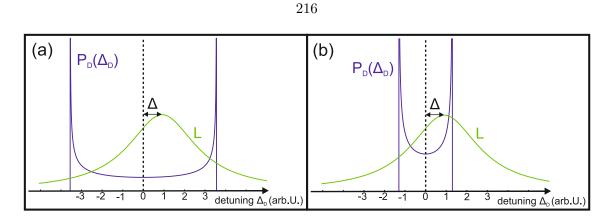

| A.1 Lorentzian line profile L and Doppler shift probability $P_D$ shown for an ion<br>with high and low motional quanta                                   |

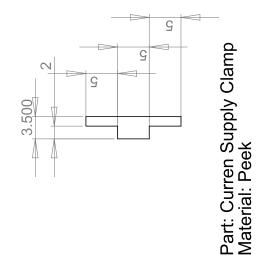

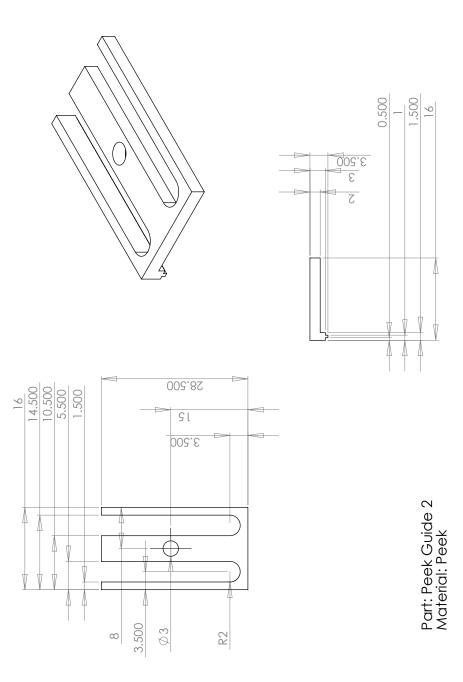

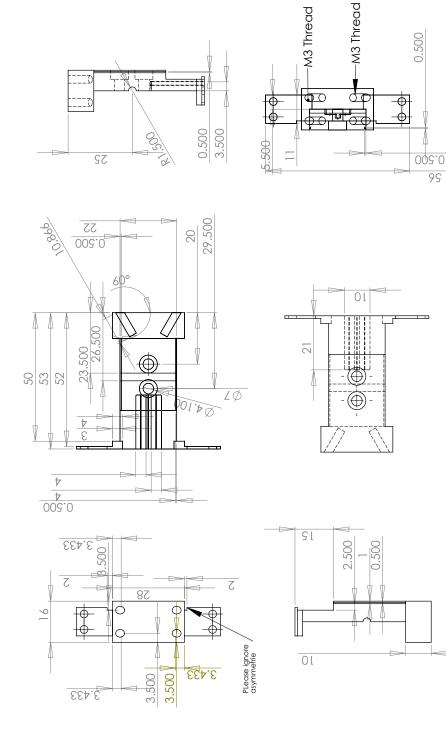

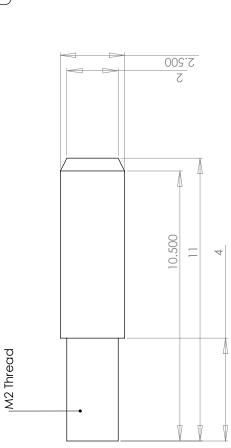

| C.1 A SolidWorks drawing for current supply clamps                                                                                                        |

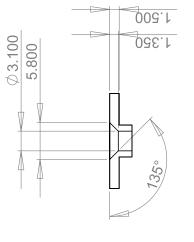

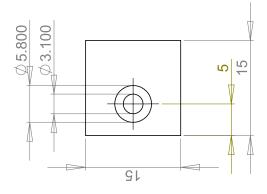

| C.2 A SolidWorks drawing for current supply structure (part 1)                                                                                            |

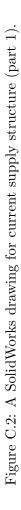

| C.3 A SolidWorks drawing for current supply structure (part 2)                                                                                            |

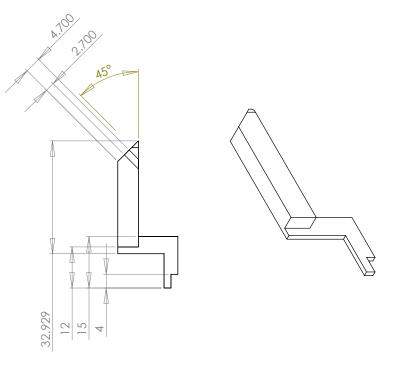

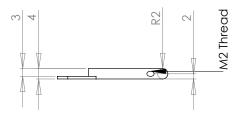

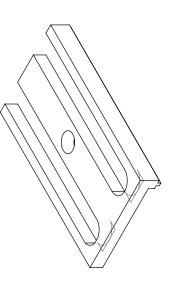

| C.4 A SolidWorks drawing for peek spacer separating the two current supply                                                                                |

| structures (part 1)                                                                                                                                       |

| C.5 A SolidWorks drawing for peek spacer separating the two current supply                                                                                |

| structures (part 2)                                                                                                                                       |

| C.6 A SolidWorks drawing for the bottom part of the thermal bridge 232                                                                                    |

| C.7 A SolidWorks drawing for the top part of the thermal bridge                                                                                           |

| C.8 A SolidWorks drawing of BNP2 spacers                                                                                                                  |

| C.9 A SolidWorks drawing of the copper chip holder                                                                                                        |

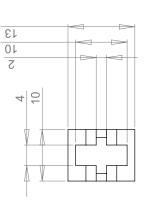

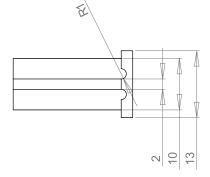

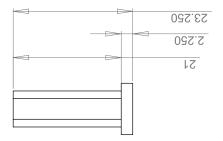

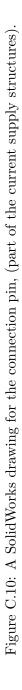

| C.10 A SolidWorks drawing for the connection pin, (part of the current supply                                                                             |

| structures). $\ldots \ldots 236$                                             |

| C.11 A SolidWorks drawing of the copper adapter                                                                                                           |

| C.12 A SolidWorks drawing of custom recessed window                                                                                                       |

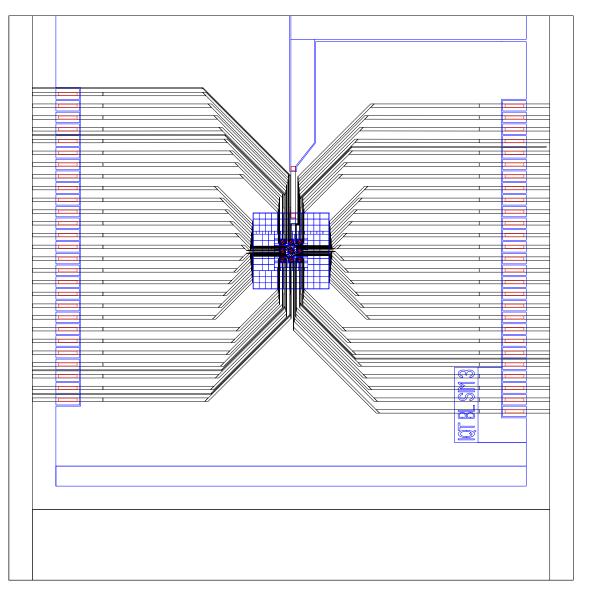

| D.1 Ion Trap Design 1: Linear ion trap, 250 $\mu$ m ion height                                                                                            |

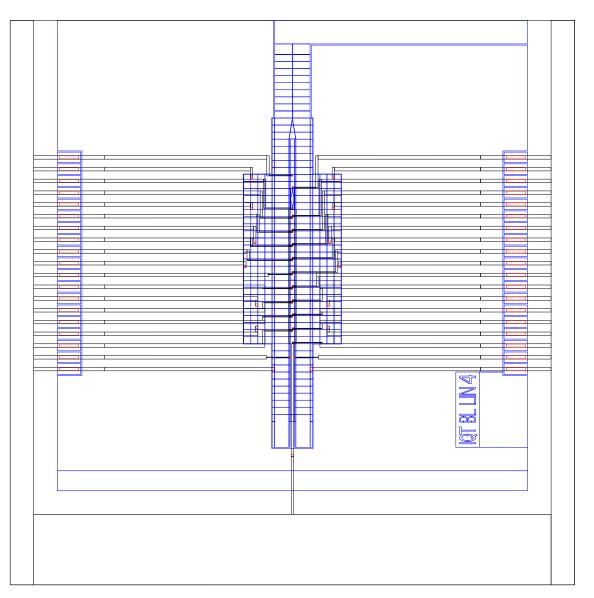

| D.2 Ion Trap Design 2: Linear ion trap with loading slot, 165 $\mu{\rm m}$ ion height 241                                                                 |

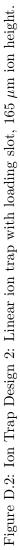

| D.3 Ion Trap Design 3: Linear ion trap with detection slot, 100 $\mu{\rm m}$ ion height 242                                                               |

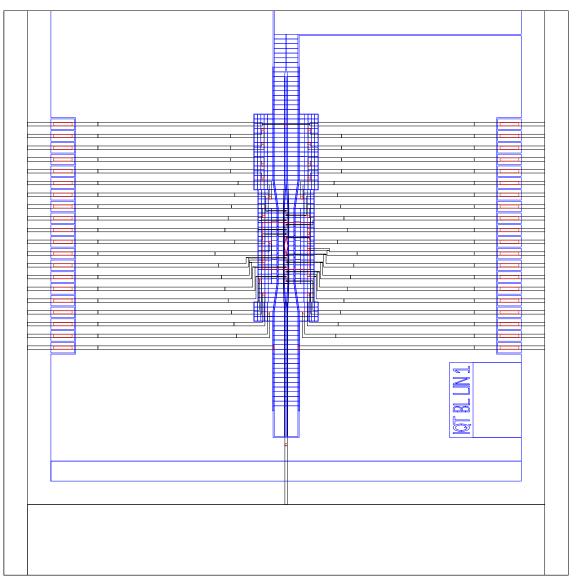

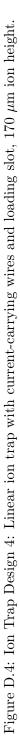

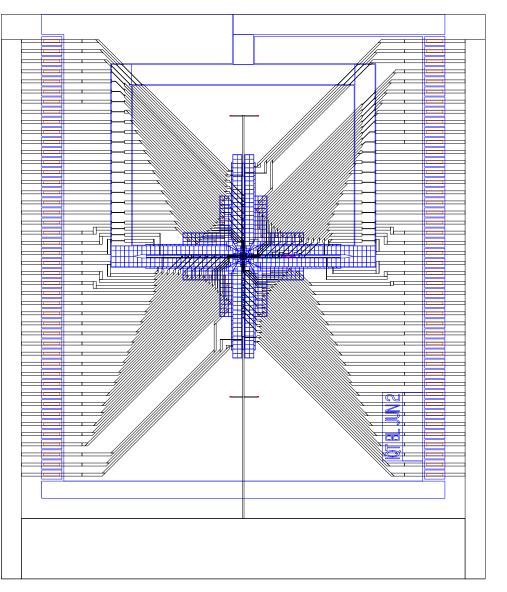

| D.4 Ion Trap Design 4: Linear ion trap with current-carrying wires and loading                                                                            |

| slot, 170 $\mu$ m ion height                                                                                                                              |

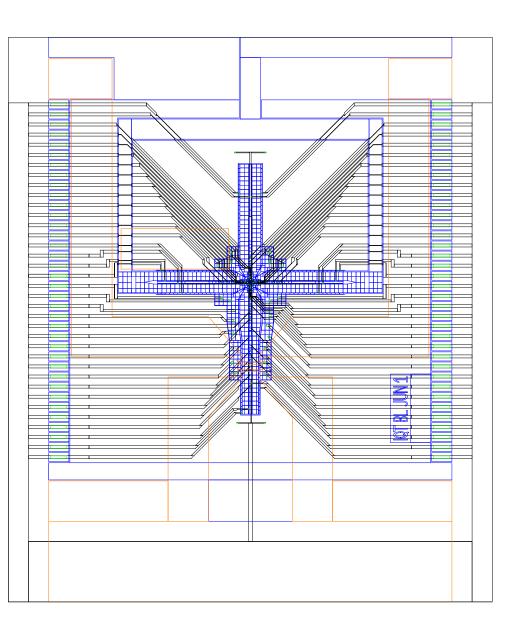

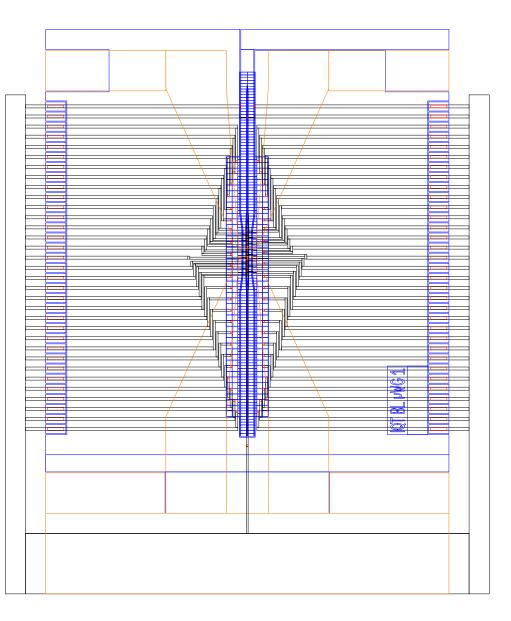

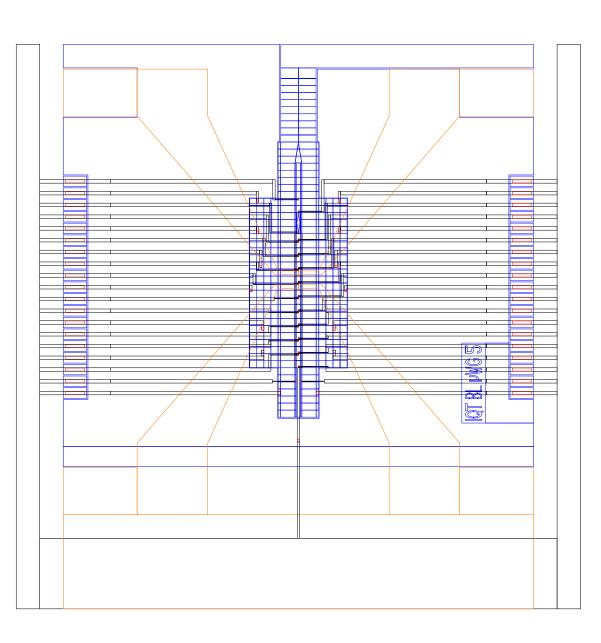

| D.5 Ion Trap Design 5: X-junction ion trap, 100 $\mu$ m ion height 244                                                                                    |

| D.6 Ion Trap Design 6: X-junction ion trap, 200 $\mu$ m ion height 245                                                                                    |

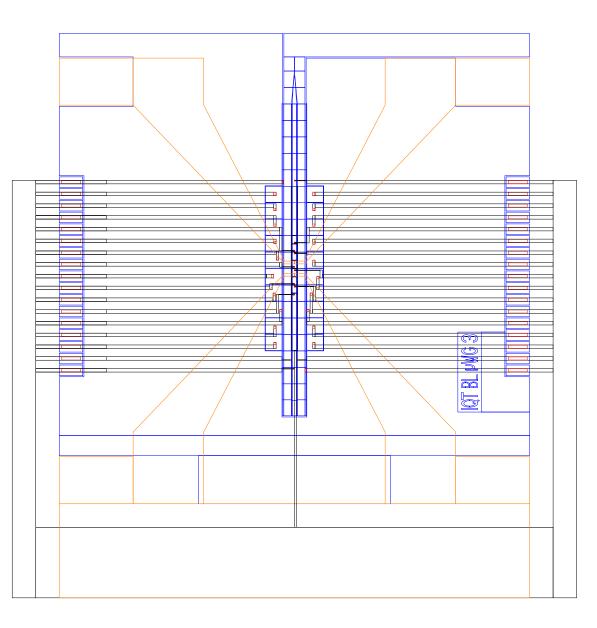

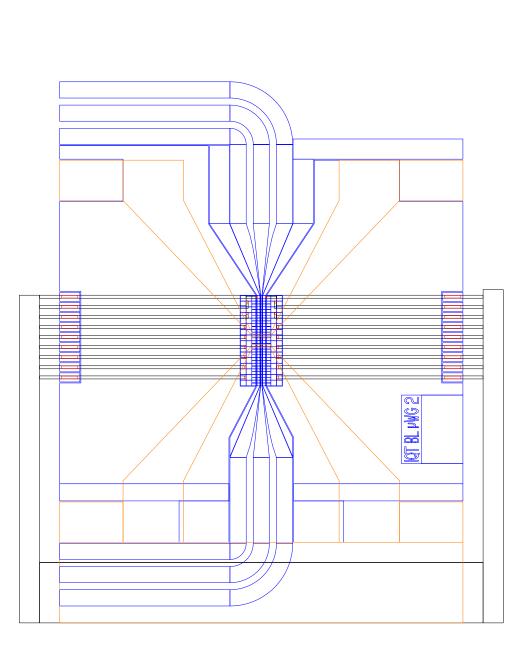

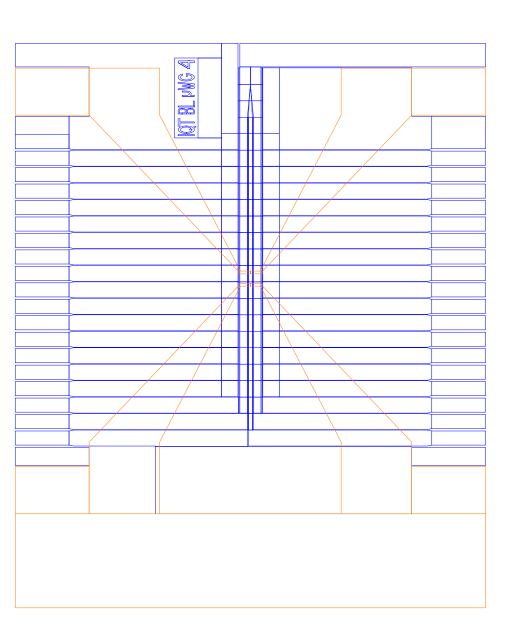

| D.7 Ion Trap Design 7: Linear ion trap with current-carrying wires, 120 $\mu {\rm m}$ ion                                                                 |

|                                                                                                                                                           |

| height                                                                                                                                                    |

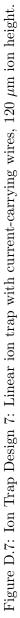

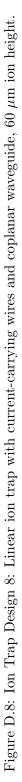

| height.246D.8Ion Trap Design 8: Linear ion trap with current-carrying wires and coplanar                                                                  |

|                                                                                                                                                           |

| D.8 Ion Trap Design 8: Linear ion trap with current-carrying wires and coplanar                                                                           |

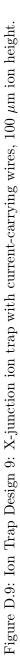

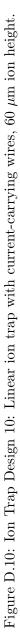

| D.10 Ion Trap Design 10: Linear ion trap with current-carrying wires, 60 $\mu {\rm m}$ ion      |

|-------------------------------------------------------------------------------------------------|

| height                                                                                          |

| D.11 Ion Trap Design 11: Two-dimensional ion trap array, 100 $\mu \rm{m}$ ion height 250        |

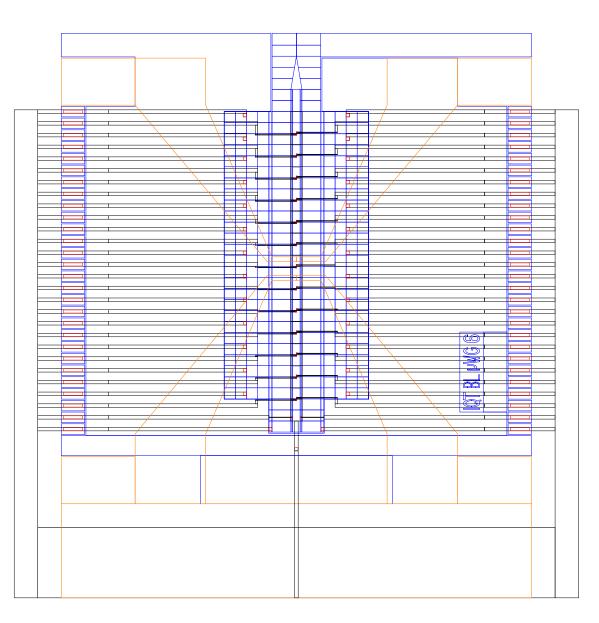

| D.12 Ion Trap Design 12: Linear ion trap with current-carrying wires, 120 $\mu{\rm m}$          |

| ion height                                                                                      |

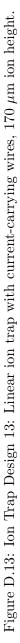

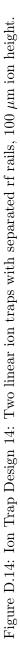

| D.13 Ion Trap Design 13: Linear ion trap with current-carrying wires, 170 $\mu{\rm m}$          |

| ion height                                                                                      |

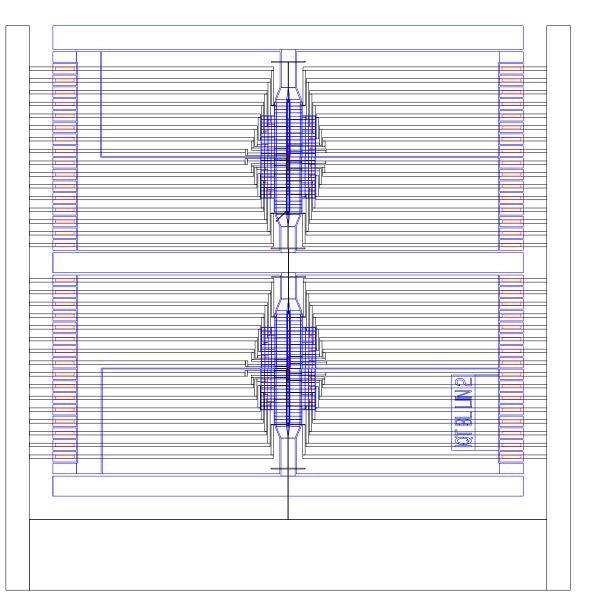

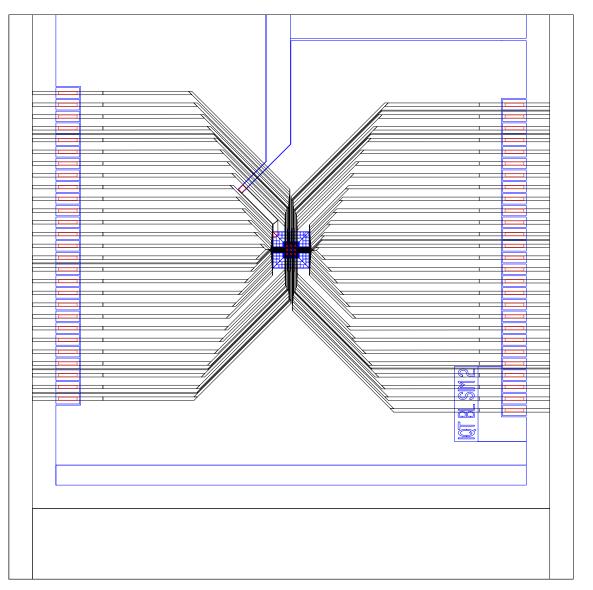

| D.14 Ion Trap Design 14: Two linear ion traps with separated rf rails, 100 $\mu{\rm m}$         |

| ion height                                                                                      |

| D.15 Ion Trap Design 15: Two-dimensional ion trap array, 50 $\mu {\rm m}$ ion height. $~$ . 254 |

| D.16 Ion Trap Design 16: Two-dimensional ion trap array, 30 $\mu {\rm m}$ ion height 255        |

### Chapter 1

## Introduction

Quantum information technology holds tremendous potential to advance research fields, computational methods and modern communication technologies. Simulations based on quantum bits (qubits) and quantum operations (entanglement gates) can be used to efficiently simulate quantum systems, impossible for classical computers, as proposed by Feynman [1] over 30 years ago. Since then many basic quantum simulations of material properties [2–8] have been realized and many different applications of quantum systems have been investigated to simulate theoretical models [9–12]. The knowledge gained from large scale quantum simulations has great potential to extend our knowledge of basic physical principles, lead to the development of more advanced theoretical models and ultimately result in new technologies and materials.

Extending Feynman's idea of universal quantum simulators Deutsch proposed a universal quantum computer [13], which can be seen as the quantum equivalent to the universal Turing machine (UTM) [14]. It can perform tasks and solve algorithms efficiently, which would be impossible for a UTM, making use of the quantum nature of the device. Consequentially many algorithms to be used by a quantum computer were proposed, including algorithms by Shor [15] and Grover [16] and many others [17–20].

Shor's algorithm allows for the efficient factorizing of large numbers and has been implemented in small scale quantum systems [21, 22]. Grover's algorithm improves the search of very large unstructured databases and has also been demonstrated in a quantum system [23]. Large scale realization of both algorithms would have great impact on today's information technology. Searching of large unstructured databases is an important part of finding relevant information in the world wide web or large metadata databases. Grover's algorithm provides a dramatic speed up compared to current classical algorithms, but not comparable to the exponential gain of Shor's algorithm [24]. The efficient factorization of large numbers would make it possible to decipher the commonly used RSA encryption technology [25], allowing most of today's encryptions to be circumvented [26].

Quantum systems also provide a method to achieve absolutely secure communication channels. Using two entangled qubits and transmitting information via quantum state teleportation results in perfectly safe communication, due to the no-cloning theorem. It states that unknown quantum states can't be cloned [27] and therefore transmitted information cannot be intercepted without detection [28, 29]. Quantum systems allowing for secure communication, based on the no-cloning theorem, have been experimentally demonstrated in the laboratory [30, 31] and recently between satellites and a ground station [32].

The tremendous achievements and possibilities of quantum systems has motivated great research efforts towards the realization and optimization of quantum simulators and universal quantum computers by many research groups in different fields of physics. Characterizing the progress of different quantum system technologies towards this goal helps to identify promising technologies and outline major goals for future developments. Such a characterization can be made by making use of the requirements placed on quantum systems to realize a universal quantum computer. D. P. DiVincenzo presented a discussion [33] summing up the requirements a system must fulfill to become a universal quantum system:

**State initializations** of the qubits in a simple fiducial state needs to be performed.

Decoherence time of qubits in the system needs to be much longer than the gate times.

Universal gates for one and two qubits operations [34].

**Readout** of any arbitrary qubit in the system.

Physical scalability with well characterized quantum bits.

Among the many quantum systems being researched, some of the most promising approaches [35] include: neutral atom systems, most prominently based on atoms trapped in optical lattices [36], magneto-optical traps (MOTs) [37] or optical cavity hybrid systems [38]; superconductor based systems with qubits making use of Josephson junctions [39–41]; photonic quantum systems based on linear optics [42, 43] or weak cross-Kerr coupling [44]; and trapped ion quantum systems [45–47], which can be grouped into

systems addressing physical scalability with the movement of trapped ions [48] or hybrid systems using ion-photon entanglement [49].

Possibly the most promising of all is the trapped ion quantum system, making use of traps providing means to store and manipulate ionized atoms, well isolated from the environment. Ion trap systems have achieved almost all of the required criteria [50,51] and allow for a physically scalable system. Robust and high fidelity **state preparation** [52] and **readout** [53–55] of qubits with long **decoherence times** [56] and fast **universal gates** [45,51,57,58] have been demonstrated. Additionally many advances in the field of error correction [59–64] have been made.

This success is based on a well developed tool kit which has its origin in the development of an electrodynamic mass spectrometer by W. Paul in 1953 [65, 66], which was also used to trap ions [67, 68] shortly after. Commonly used ion trap technologies are the Paul [65, 66] and Penning traps [69, 70]; only Paul traps will be considered for scalable ion trap systems in this thesis. To improve the accuracy of spectroscopy measurements, laser cooling of trapped ions was developed [71, 72], followed by the first experimental demonstration of a two qubit quantum gate [45] and theoretical work towards the realization of large scale ion trap architectures [73].

A theoretical discussion of the principles of ion traps, the atomic structure of the ion used and basics of quantum operations will be given in chapter 2. Asymmetric ion trap geometries, stable trapping and laser cooling of ions will be discussed in detail. The defining characteristic of asymmetric (also known as surface) ion traps is that all electrodes are placed below the trapping zone in one plane. The electrode geometry is asymmetric with respect to the trap centre, unlike symmetric traps where the electrodes are placed symmetrically in planes above and below the trapping centre. Asymmetric traps have the disadvantage of lower trap depth compared to symmetric traps with similar applied potentials and ion electrode distances. Due to the electrode configuration they allow laser access in almost the entire plane parallel to the surface and also provide free optical access to the trapped ion from above the surface. Also the fabrication of asymmetric traps is based on standard microfabrication technologies without the need for extremely thick dielectric layers between electrodes [74], giving them an advantage in relative ease of fabrication.

In chapter 3 the operation of a macroscopic ion trap and the necessary experimental setup will be discussed. I then outline a number of experiments performed in the described trap,

including trapping of different isotopes, measurement of the secular frequencies in all trap axes and determination of the heating rate of the system.

Chapter 4 will give an overview of microfabricated surface ion traps, based on work done by the author for [75]. Important considerations concerning the electrical properties of an ion trap will be discussed. Causes of micromotion and models explaining the anomalous heating found in ion traps will be outlined. Then an overview of fabrication technologies commonly used in trap fabrications will be discussed and the advantages, disadvantages and underlying problems of these different processes will be analyzed. A new fabrication process developed by the author more suitable for the desired trap structures will also be introduced.

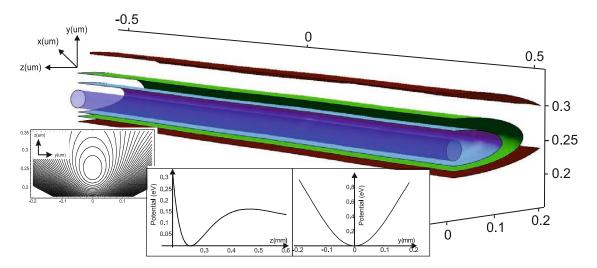

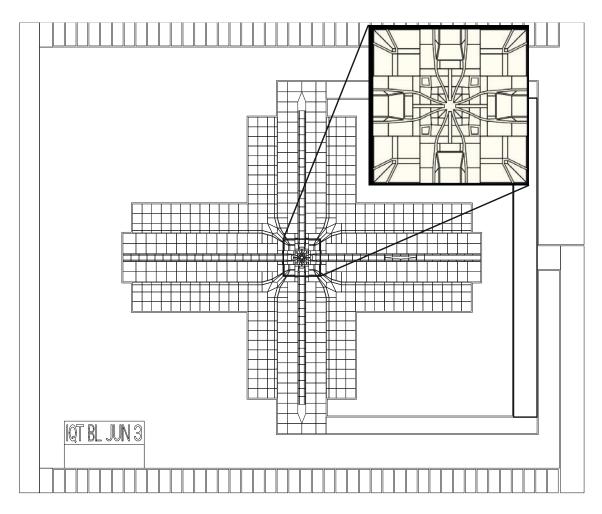

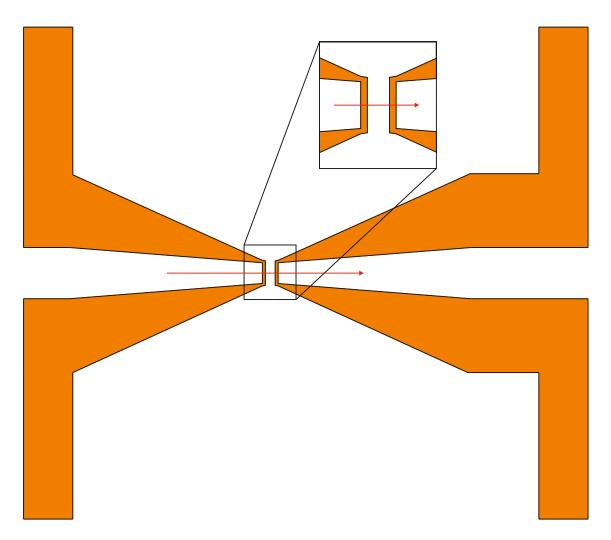

Chapter 5 will present a concept for a scalable ion quantum system. Physical scalability of ion trap quantum systems came into reach after the development of the first microfabricated ion trap [76,77] and the demonstration of shuttling of ions through junctions [78-81]shortly after. Gates making use of strong magnetic field gradients and microwave transitions have been realized recently [82, 83] and hold the promise of dramatically improving the scalability of the ion trap quantum systems [84]. In chapter 5 entanglement requirements and error rates of quantum error codes that are used to form logical qubits will be analyzed. Logical qubits are made up of a large number of physical qubits and use an error correction code to perform  $\sim 10^{16}$  error protected quantum operations, enough for any quantum algorithm or simulation proposed so far [85]. Depending on the fidelity rate of physical qubit operations more than 1000 physical qubits will be necessary to achieve one logical qubit. Based on the requirements of the used error correction code a scalable ion trap architecture will be presented in 5. The architecture is based on a two-dimensional array of X-junctions with entanglement zones as illustrated in Fig. 1.1. Individual building blocks of the array will be discussed in detail and required technology developments identified.

Based on a newly developed fabrication process detailed ion trap designs will be presented and resulting mask designs will be outlined in chapter 6. Individual design steps, the design process and process limitations will be described. The optimization of an X-junction electrode for minimal rf barrier height, development of current-carrying wire structures intended to generate large magnetic field gradients and designs motivated by the scalable architecture outlined in chapter 5 will be presented. Trapping parameters and numerically simulated electric fields of the traps in question will be described.

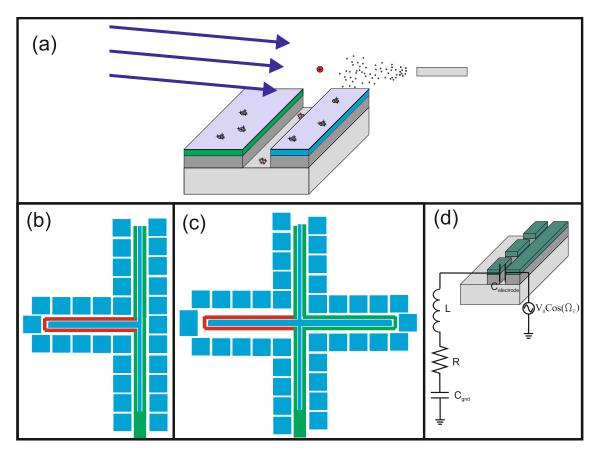

Figure 1.1: Illustration showing a two-dimensional trapping array made up of X-junctions forming a two-dimensional grid. Ions can be shuttled from one junction arm to another and joined with ions from other junctions in entanglement zones. In the inset a more detailed view of an entanglement gate based on magnetic field gradients is given.

In chapter 7 additions to the experimental system, including an argon sputter gun, an in-vacuum system designed to transport heat away from ion traps with current-carrying wires and a new multichannel voltage control system, will be presented. The argon plasma source can be used to perform *in situ* cleans of the trap electrodes, which has been shown to dramatically reduce the heating rate in ion traps [86, 87]. The in-vacuum heat transport system is required to operate traps with current-carrying wires without overheating them. Additionally the heat bridge should also allow the trap to be cooled to cryogenic temperatures from the outside of the vacuum system. The voltage control system is based on low-noise components and can generate high speed, high voltage arbitrary waveforms intended for ion shuttling.

Lastly the process optimization and microfabrication of the developed ion trap designs will be presented in chapter 8. The novel fabrication process was developed at the Southampton Nanofabrication Centre and makes use of highly thermally conductive diamond substrates and combines it with thick copper tracks embedded in the substrate. Individual process steps will be described in detail and results presented.

## Chapter 2

## Ion Trapping and the Yb Ion

In this chapter the basic electromagnetic principles behind the operation of Paul traps [67] will be explained. Paul traps with surface trap electrode geometries, where all electrodes are placed in one plane [75, 77], will be investigated in more detail. Analytical and numerical methods to obtain the electric fields for these traps will be given and results presented. Laser cooling and atomic levels of the Ytterbium (Yb) ion will be discussed and the requirements to perform quantum gates will be briefly outlined. The fundamentals of microfabricated ion trap designs and experiments were reviewed in 'Microfabricated ion traps' [75] and this chapter is partially based on work for this publication.

#### 2.1 Electric Fields and Ion Motion in Paul Traps

Gauss's Law states that the divergence of an electric field  $\mathbf{E}(\mathbf{x})$  in free space must be zero  $\nabla \cdot \mathbf{E}(\mathbf{x}) = 0$ , with  $\mathbf{E}(\mathbf{x}) = \nabla \cdot \Phi(\mathbf{x})$  resulting in  $\nabla^2 \Phi(\mathbf{x}) = 0$ , which is the Laplace equation and is also stated by Earnshaw's Theorem [88]. As a direct result the electrostatic force  $\mathbf{F}(\mathbf{x})$  stemming from an electric potential  $\Phi(\mathbf{x})$  must be divergenceless and cannot hold a point charge in a stable equilibrium. Looking at the two-dimensional potential Fig. 2.1 (b) of hyperbolic shaped electrodes Fig. 2.1 (a) one can see that a saddle potential with confining saddle points in one direction and unstable points in the other is generated. Stable trapping of ions in all three dimensions is not possible using solely static electric potentials.

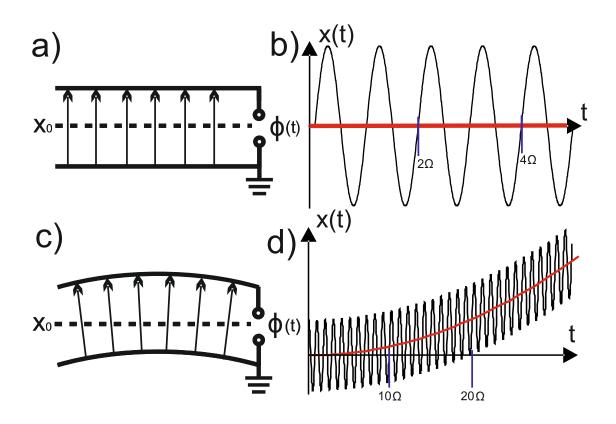

To circumvent this limitation an alternating potential  $\phi(t)$  is applied to the electrodes, which results in a rotation of the created saddle potential and as will be shown later in this

Figure 2.1: (a) Hyperbolic shaped electrodes, opposite plates have the same potential  $\phi$  and obverse plates will have the same potential with inverse polarity  $-\phi$ . (b) Twodimensional saddle potential with stable trapping in one direction.

chapter, when averaged over time this results in a stable trapping potential as shown Fig. 2.2. Using this, stable trapping of ions in two [65] or three dimensions [67] is possible. Most modern ion traps [75,89,90] use a combination of two-dimensional confinement provided by an oscillating potential  $\Phi(t)$  and confinement in the third dimension via static potentials.

Figure 2.2: Time averaged trapping potential generated by an alternating potential  $\phi(t)$  applied to the hyperbolic electrodes.

#### 2.1.1 Ion Motion in the Pseudopotential Approximation

To investigate how the ion behaves inside such an electric potential we will derive and solve the equations of motion for the ion. The calculations will follow the derivations presented in [66], [70] and [91].

We start with a simple homogenous electric field  $E_h$  generated by two parallel plates as shown in Fig. 2.3 (a) with an alternating potential  $\phi(t) = V \cos(\Omega t) + U$  applied to one of the plates, where  $\Omega$  is the drive frequency, V the voltage amplitude of the alternating potential and U a static voltage added as an offset to the oscillating voltage. The one dimensional equation of motion of the trapped ion of mass m and charge e in the x-axis is then:

$$m\ddot{x}(t) - eE_h\cos\left(\Omega t\right) + eE_s = 0 \tag{2.1}$$

The static electric field  $E_s$  arises from the static voltage offset U applied to the electrodes and can be kept at zero in most ion trap experiments [89]. For most of the following derivation  $E_s$  will therefore be neglected. The solution for equation 2.1 can be gained by direct integration to be

$$x(t) = x_0 - a\cos\left(\Omega t\right) for U = 0$$

(2.2)

with a being the constant amplitude of the oscillation equal to  $a = \frac{eE_h}{m\Omega^2}$ . Plotting the ion motion inside the parallel plates Fig. 2.3 (b) it can be seen that averaged over time there is no force acting on the ion as it is only oscillating back and forth, returning to the starting point  $x_0$  after one oscillation period Fig. 2.3 (b).

A non-zero time averaged force acting on the ion is required for trapping and can be obtained by slightly bending the plates Fig. 2.3 (c). The generated electric field becomes inhomogeneous  $E_{ih}(x)$ . Corresponding differential equations of motion can generally not be solved analytically and require numerical solutions [91].

In the present case of a weakly inhomogeneous field a few assumptions and approximations can be made to solve the equation without relying on numerical techniques. The field variations of  $E_{ih}(x)$  in x have to be smooth and the frequency  $\Omega$  has to be high enough to keep the amplitude  $a = \frac{eE_{ih}}{m\Omega^2}$  of the oscillation small compared to the motion of the ion caused by the inhomogeneity of the field. We can then replace  $E_h$  in equation 2.1 with  $E_{ih}(x)$  and solve the new equation by superimposing a slow drift term  $x_s$  with a fast oscillating term  $x_f = -a(t) \cos(\Omega t)$ , which results in

Figure 2.3: (a) Parallel plates with applied potential  $\phi$  and corresponding E field. (b) Ion motion x(t) vs time and the time averaged motion in red. (c) Slightly bent parallel plates with the same applied potential  $\phi$  and now inhomogeneous electric field. (d) Ion motion x(t) vs time in the inhomogeneous field and time averaged motion in red.

$$x(t) = x_s(t) - a(t)\cos\left(\Omega t\right) \tag{2.3}$$

with the now time-dependent amplitude a(t). We then approximate the inhomogeneous electric field  $E_{ih}(x)$  with a 1st order Taylor Series expansion:

$$E_{ih}(x_s - a(t)\cos\left(\Omega t\right)) = E_{ih}(x_s) - a(t)\frac{\partial(E_{ih}(x_s)\cos\left(\Omega t\right))}{\partial x}$$

(2.4)

Due to the assumed slow variation of the field we can also assume that  $\dot{a} \ll \Omega a$  and  $\ddot{x}_s \ll \Omega \dot{x}_s$ . Substituting equation 2.3 and 2.4 into the equation of motion 2.1 results in the following equation for the ion motion inside the slightly bent parallel plates:

$$m\ddot{x}_s(t) + m\Omega^2 a(t)\cos\left(\Omega t\right) = eE_{ih}(x_s)\cos\left(\Omega t\right) - ea(t)\frac{\partial(E_{ih}(x_s)\cos^2\left(\Omega t\right))}{\partial x}$$

(2.5)

Assuming that the amplitude a(t) varies in time only due to the motion of the ion along  $x_s(t)$  we can replace a(t) with  $a(x_s)$ . Now if we time average the equation over one period with,  $\langle \cos^2(\Omega t) \rangle = 1/2$  and  $\langle \cos(\Omega t) \rangle = 0$  equation 2.5 takes the form:

$$\langle m\ddot{x}_s(t)\rangle = -\frac{1}{2}ea(x_s)\frac{\partial E_{ih}(x_s)}{\partial x}$$

(2.6)

Substituting  $a(x_s) = \frac{eE_{ih}(x_s)}{m\Omega^2}$  and using the general vector analysis relation,

$$\mathbf{E}\nabla\mathbf{E} = \frac{1}{2}\nabla(\mathbf{E} * \mathbf{E}) \tag{2.7}$$

we can further simplify equation 2.6 to:

$$\langle m\ddot{x}_s(t)\rangle = -\frac{e^2}{4m\Omega^2}\frac{\partial E_{ih}^2}{\partial x}$$

(2.8)

The force  $F = m\ddot{x}_s(t)$  arises from the alternating inhomogeneous electric field  $E_{ih}$  and its direction is determined by the gradient  $\frac{\partial E_{ih}^2}{\partial x}$ . The electric force on the ion will always point towards the weakest points of the field  $E_{ih}$ . Making the following substitution

$$\psi(x_s) = \frac{e^2}{4m\Omega^2} E_{ih}^2 \tag{2.9}$$

the equation of motion can be brought into the form,

$$\langle m\ddot{x}_s(t)\rangle = -\frac{\partial\psi(x_s)}{\partial x}$$

(2.10)

The time-independent potential  $\psi(x_s)$  describes the time averaged ion motion Fig. 2.3 (d) for the discussed case. This effective potential  $\psi$  is commonly called the pseudopotential [70], and also includes the neglected static term from equation 2.1, with  $E_s = -\frac{\partial \Phi_s}{\partial x}$  and  $E_{ih} = -\frac{\partial \Phi_{ih}}{\partial x}$  taking the form:

$$\psi(x_s) = \frac{e^2}{4m\Omega^2} \frac{\partial \Phi_{ih}^2}{\partial x} + e\Phi_s \tag{2.11}$$

The solution to the equation of motion is now trivial as the pseudopotential is timeindependent and the corresponding ion motion is illustrated in Fig. 2.3 (d). If the solution for the slow drift term  $x_s$  is overlaid with the fast oscillating term  $x_f = -a(t) \cos(\Omega t)$ , where a(t) represents the time-dependent amplitude of the oscillation in the inhomogeneous electric field, the motion becomes the oscillating trajectory shown in Fig. 2.3 (d). Although the introduced pseudopotential was only derived for one dimension it can also be generalized to three dimensions, as demonstrated in [70, 92, 93].

#### 2.1.2 Mathieu Equations and Stability Parameters

We now come back to the inhomogeneous saddle potential presented in Fig. 2.2 created by the two-dimensional hyperbolic electrodes shown in Fig. 2.1 (a) and derive the equations of motion for an ion trapped in this potential. The hyperbolic potential allows for the equations of motion to be solved analytically and a detailed description of the trapped ion motion without approximations can be made. The following derivations are based on derivations presented in [66]. We start with the general three-dimensional electric quadrupole potential:

$$\Phi = \frac{\phi(t)}{2r_0^2} (\alpha x^2 + \beta y^2 + \gamma z^2)$$

(2.12)

Where  $\phi(t)$  is the oscillating potential applied to the hyperbolic electrodes,  $r_0$  is the distance between trap centre and the closest electrode point, see Fig. 2.2 (b). In the present case of a two-dimensional potential the general quadrupole equation can also be

simplified with  $\gamma = 0$  and to satisfy Laplace's equation  $\nabla \cdot \Phi = 0$  we set  $\alpha = 1 = -\beta$ . Consequentially opposite plates will be kept at potential  $\phi(t)$  and obverse plates will have the same potential with inverse polarity  $-\phi(t)$  [65]. The resulting two-dimensional inhomogeneous hyperbolic potential then takes the form:

$$\Phi = \frac{\phi(t)}{2r_0^2} (x^2 - y^2) \tag{2.13}$$

We can write the applied potential as  $\phi_0(t) = U + V \cos(\Omega t)$ ,  $\Omega$  is again the drive frequency, V the alternating voltage amplitude and U the static offset. The force acting on the trapped ion, also known as pondermotive force, can be derived as  $\mathbf{F} = -e\nabla\Phi(x, y, t)$ . When time averaged, the force  $\mathbf{F}$  will not vanish due to the inhomogeneous nature of  $\Phi$ and will have a net component pointing towards the weakest region of the potential, which in this case is the centre of the trap [66]. Considering that the movement of the ion in the x and y direction is uncoupled, we can then write the equations of motion for the trapped ion as,

$$\ddot{x}(t) + \frac{e}{mr_0^2} (U - V\cos(\Omega t))x = 0$$

(2.14)

and

$$\ddot{y}(t) + \frac{e}{mr_0^2} (U - V\cos{(\Omega t)})y = 0$$

(2.15)

These equations are uncoupled linear differential equations of second order with a periodic coefficient  $(\cos(\Omega t))$ , which puts them in the category of Mathieu equations [94, 95]. The general Mathieu equation has the form:

$$\frac{d^2i}{d\zeta^2} + (a_i - 2q_i\cos(2\zeta))i = 0$$

(2.16)

If we make the following substitutions,

$$i = [x, y], \ a_x = -a_y = \frac{4eU}{mr_0^2\Omega_T^2}, \ q_x = -q_y = \frac{2eV}{mr_0^2\Omega_T^2}, \ \zeta = \frac{\Omega_T^2 t}{2}$$

(2.17)

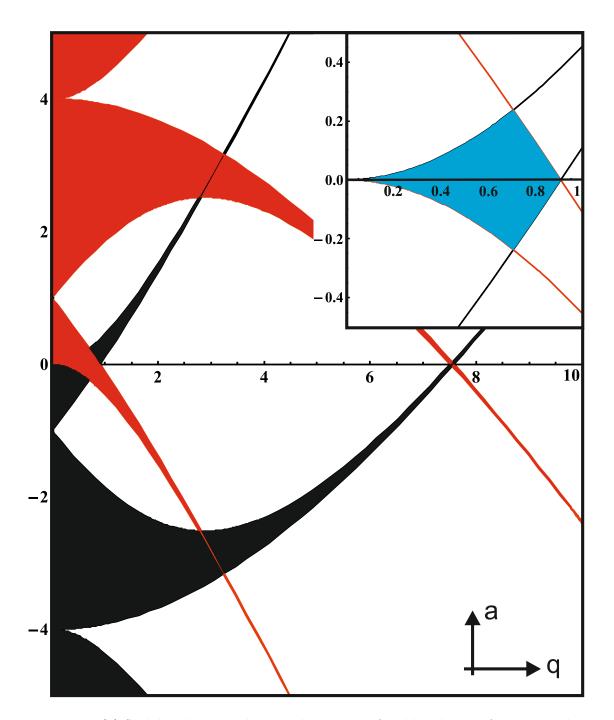

the equations of motion are brought into the same form. Mathieu equations have an infinite number of solutions, but only stable periodic solutions result in trapping of ions. Other solutions would lead to the loss of a trapped ion. The Floquet theorem [95] can be used to obtain stable solutions which are illustrated as stability regions in the a and q space Fig. 2.4. The marked areas represent regions, where a and q give stable periodic solutions, the region boundaries represent periodic but unstable solutions. Where regions of stability for the x and y motion overlap, stable trapping of the ion is possible, further illustrated in the inset of Fig. 2.4.

For the case of  $a \neq 0$ , where a static offset voltage U is applied to the electrodes, a solution for x and y is given in [89] for the region  $a_i < q_i^2 << 1, i \in x, y$ . An approximation for the more common case of  $a_i = 0$  and  $q_i^2 << 1$ ,  $i \in x, y$  can be made and we can write the equation of motion in the x-axis as [75],

$$x(t) = x_0 \cos(\omega_x t) \left[1 + \frac{q_x}{2} \cos(\Omega t)\right]$$

(2.18)

where  $\omega_x$  is the so-called secular frequency in the x-axis and equal to:

$$\omega_x = \frac{\Omega}{2} \sqrt{a_x + \frac{q_x^2}{2}} \tag{2.19}$$

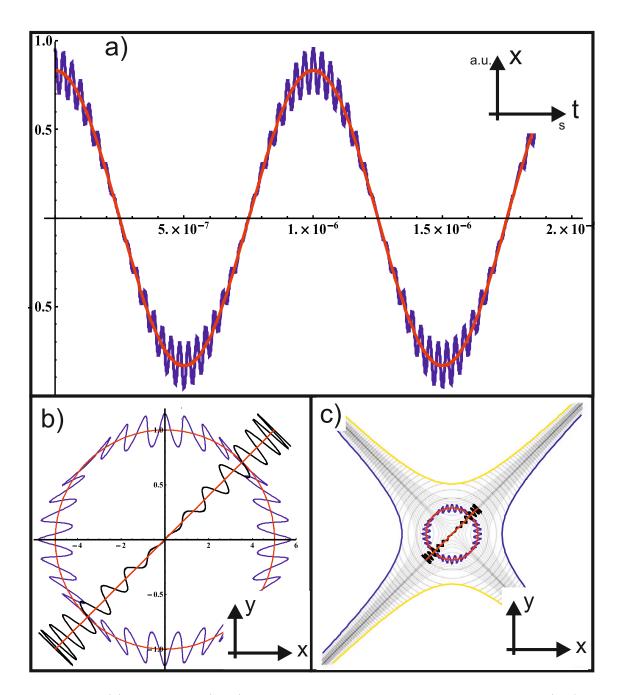

Plotting the resulting motion versus time in Fig. 2.5 (a) illustrates that the ion motion consists of a large oscillation known as the secular motion, overlaid with a faster oscillating micromotion. The micromotion oscillating with frequency  $\Omega$ , the drive frequency, is caused by the ion feeling the fast alternating potential, whenever the ion is not at the nil of the potential. This micromotion is commonly called intrinsic micromotion. When the ion is pushed out of the rf nil by a static potential we speak of extrinsic micromotion.

Comparing the solution for x(t) with the solution 2.3 used to solve the ion's equation of motion in an inhomogeneous electric field in section 2.1.1, we can see that micromotion corresponds to the fast oscillating term  $x_f(t) = x_0 \cos(\omega_x t) \frac{q_x}{2} \cos(\Omega t)$ . Due to the confining nature of the hyperbolic quadrupole potential the slow drift term in equation 2.3 is now an oscillation around the trap center. In Fig. 2.5 (b) the x and y movement during one oscillation period  $\Delta t = \frac{1}{\omega_x}$  inside the trapping potential shown in 2.5 (c) is plotted for different starting points. The plot illustrates the oscillation close to the centre and also the increase in micromotion with distance from the center.

Figure 2.4: (a) Stability diagram showing the regions of stable solutions for motion along the x-axis (red) and y-axis (black) in a, q space. The inset (b) shows the main stability region for both axes marked as blue.

Figure 2.5: (a) Ion motion (blue) along the x-axis vs time, the large oscillation (red) is overlaid with a higher frequency micromotion. (b) Ion motion in x and y-axis during one oscillation period for two different starting points. The increase of micromotion with distance from the centre becomes visible. (c) Illustration of the same motion with the trap electrodes and potential (not to scale).

Looking at the previously introduced time-averaged harmonic pseudopotential for this case given in [89] and shown in Fig. 2.2:

$$\psi(r) = \frac{1}{2q} m \omega_r^2 (x^2 + y^2) \tag{2.20}$$

Making the approximation  $\omega_r \sim \omega_x$ , that the secular frequency is similar<sup>1</sup> in x and y-axis, the equation of motion in the pseudopotential approximation, using equation 2.1 is equal to,

$$\ddot{x}(t) = \omega_x^2 x \tag{2.21}$$

As expected the slow oscillating drift term  $x_s$  from equation 2.3 is a solution to this equation. The pseudopotential approximation allows for an accurate description of the secular motion and will be used almost exclusively for the following trap simulations. Nevertheless the stability parameters of the Mathieu equation still need to be calculated and have to be inside a stable trapping region.

## 2.1.3 Analytical Simulations of Electric Fields in Surface Traps

In the previous discussion of the ion motion we used electrode geometries with known analytic functions describing the electric fields. Unfortunately most ion trap geometries don't have analytic functions describing the trapping fields. Numerical simulations are required to find the electric fields and commonly used methods will be discussed in section 2.1.4. Fortunately, for surface trap geometries an approximation can be made that provides a method to obtain the electric field analytically. Such analytical methods were presented in [96] and [97].

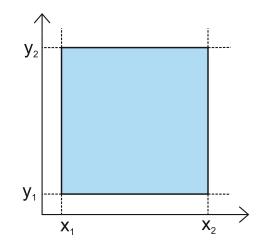

### **Deriving Electric Fields of Surface traps**