#### A University of Sussex PhD thesis

Available online via Sussex Research Online:

http://sro.sussex.ac.uk/

This thesis is protected by copyright which belongs to the author.

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Please visit Sussex Research Online for more information and further details

# An Investigation into Multi-Spectral Excitation Power Sources for Electrical Impedance Tomography

By

Tabassum-Ur-Razaq Qureshi

A thesis submitted for the degree of Doctor of Philosophy

Biomedical Engineering, School of Engineering and Informatics University of Sussex, Brighton, UK

November 2017

|   | <br>     |  |

|---|----------|--|

| 1 | laration |  |

|   | шагашОп  |  |

| I hereby declare that this thesis has no | ot been and will not be, submitted in |

|------------------------------------------|---------------------------------------|

| whole or in part to another University   | for the award of any other degree.    |

Signature: .....

Tabassum-Ur-Razaq Qureshi

#### **UNIVERSITY OF SUSSEX**

#### TABASSUM-UR-RAZAQ QURESHI- PHD ENGINEERING

# AN INVESTIGATION INTO MULTI-SPECTRAL EXCITATION POWER SOURCES FOR ELECTRICAL IMPEDANCE TOMOGRAPHY

#### **ABSTRACT**

Electrical Impedance Tomography is a non-invasive, non-ionizing, non-destructive and painless imaging technology that can distinguish between cancerous and non-cancerous cells by reproducing tomographic images of the electrical impedance distribution within the body. The primary scope of this thesis is the study of hardware modules required for an EIT system. The key component in any EIT system is the excitation system. Impedance measurement can be performed by applying either a current or voltage through emitting electrodes and then measuring the resulting voltages or current on receiving electrodes.

In this research, both types of excitation systems are investigated and developed for the Sussex EIM system. Firstly, a current source (CS) excitation system is investigated and developed. The performance of the excitation system degrades due to the unwanted capacitance within the system. Hence two CS circuits: Enhance Howland Source (EHS) and EHS combined with a General impedance convertor (GIC: to minimise the unwanted capacitance) are evaluated. Another technique (guard-amplifier) has also been investigated and developed to minimise the effect of stray capacitance. The accuracy of both types of CS circuits are evaluated in terms of its output impedance along with other performance parameters for different loading conditions and the results are compared to show their performance. Both CS circuits were affected by the loading voltage problem. A bootstrapping technique is investigated and integrated with both CS circuits to overcome the loading voltage problem. The research shows that both CS circuits were unable to achieve a high frequency bandwidth (i.e. >10MHz) and were limited to 2-3MHz. Alternatively, a discrete components current source was also investigated and developed to achieve a high frequency bandwidth and other desirable performance parameters. The research also introduces a microcontroller module to control the multiplexing involved for different CS circuit configurations via serial port interface software running on a PC.

For breast cancer diagnosis, the interesting characteristics of breast tissues mostly lie above 1MHz, therefore a wideband excitation source covering high frequencies (i.e. ≥1-10MHz) is required. Hence, a second type of the excitation system is investigated. A constant voltage source (VS) circuit was developed for a wide frequency bandwidth with low output impedance. The research investigated three VS architectures and based on their initial bandwidth comparison, a differential VS system was developed to provide a wide frequency bandwidth (≥10MHz). The research presents the performance of the developed VS excitation system for different loading configurations reporting acceptable performance parameters. A voltage measurement system is also developed in this research work. Two different differential amplifier circuits were investigated and developed to measure precise differential voltage at a high frequency.

The research reports a performance comparison of possible types of excitation systems. Results are compared to establish their relationship to performance parameters: frequency bandwidth, output impedance, SNR and phase difference over a wide bandwidth (i.e. up to 10MHz). The objective of this study is to investigate which design is the most appropriate for constructing a wideband excitation system for the Sussex EIM system or any other EIT based biomedical application with wide a bandwidth requirement.

## Acknowledgement

Before anything, first I would like to thank Almighty ALLAH for giving me the PhD study opportunity and courage during the whole research process. I am very thankful to my parents for always being supportive for me and their guidance is invaluable. I am deeply thankful to my younger brothers Junaid, Jahanzaib and sister Hina, for their love and support throughout my life.

I am sincerely grateful to my supervisors: Prof. Chris Chatwin and Dr. Thomas Bach for their guidance and support during my studies. I am extremely thankful to Prof. Chris Chatwin for his generous support during my difficult study stages, without his invaluable help, guidance and substantial encouragement; this thesis would not have been accomplished. I appreciate the help and guidance given by Dr. Thomas Bach during my study at the University of Sussex, which has benefited a great deal from his suggestions. I would also like to thank all the biomedical research group colleagues and friends, who have given support and help during my research studies.

I sincerely acknowledge my sponsor, COMSATS Institute of Information Technology, Islamabad Pakistan, for awarding me PhD scholarship under the faculty development program. Without their generosity, this degree would not be an easy task to complete.

I am thankful to all my friends at Sussex, who remained very supportive and cooperative throughout my PhD studies. A wholehearted thanks to my special friends: Bushra Hassan, Rana Bilal, Akber Gardezi, Mukesh Khatwani, Zahid, for always being helpful whenever I asked for assistance. Without them, this journey would not have been possible. We had a best time together and I wish them all the best in their career and life ahead.

The most important of all, I would like to pay my sincere thanks to my soul-mate and life-partner, Uzma. I dedicate this thesis to you. I deeply appreciate your support and sacrifice during my studies abroad. Thanks for always being supportive whenever I needed you, cheering me up during my studies ups and downs. I also acknowledge my children: Hadiah, Faiq and Inshal, sacrifice whom I am not able to spend much time due to my studies. I am sure they must have missed me a lot during these days, but want to tell that I also have significantly missed their presence here in the UK.

Lastly, I am thankful to all my extended family members who have always prayed for my success during my stay at the University of Sussex.

# Table of Contents

| Declaration                                 | ii   |

|---------------------------------------------|------|

| Abstract                                    | iii  |

| Acknowledgement                             | iv   |

| List of Publications                        | xi   |

| List of Acronyms                            | xiii |

| List of Symbols                             | XV   |

| List of Figures                             | xvi  |

| List of Tables                              | XX   |

| Chapter 1                                   | 1    |

| 1.1 Introduction                            | 1    |

| 1.2 What is Cancer?                         | 2    |

| 1.2.1 Types of Cancer                       | 3    |

| 1.2.1.1 Carcinoma                           | 4    |

| 1.2.1.2 Sarcoma                             | 4    |

| 1.2.1.3 Leukaemia                           | 4    |

| 1.2.1.4 Lymphomas                           | 5    |

| 1.2.2 Cancer Staging and Grading            |      |

| 1.2.2.1 The TNM Staging System              | 6    |

| 1.2.2.2 The Number Staging System           | 6    |

| 1.2.2.3 Cancer Cell Grading                 | 7    |

| 1.3 Breast Cancer and its Stages            | 7    |

| 1.3.1 Breast Cancer                         | 7    |

| 1.3.2 Breast Cancer Stages                  | 9    |

| 1.4 Cancer Diagnosis Method                 | 10   |

| 1.5 Imaging Based Cancer Diagnosis          | 12   |

| 1.5.1 X-ray Mammography Scan                | 13   |

| 1.5.2 Magnetic Resonance Imaging (MRI) Scan | 14   |

| 1.5.3 Ultrasound / Sonography Scan          | 15   |

| 1.5.4 Nuclear Medicine Imaging Scan               | 16 |

|---------------------------------------------------|----|

| 1.5.5 Electrical Impedance Tomography (EIT) Scan  | 17 |

| 1.6 Research Objectives and Achievements          | 18 |

| 1.7 Thesis Organisation                           | 20 |

| Chapter 2                                         | 22 |

| 2.1 Introduction                                  | 22 |

| 2.2 Bio-impedance of a Biological Tissue          | 22 |

| 2.3 Electrical Impedance Tomography               | 27 |

| 2.3.1 Background of EIT                           | 27 |

| 2.3.2 Applications of EIT                         | 28 |

| 2.3.3 Brief History of EIT in Medical Application |    |

| 2.4 EIT Theory and System Components              |    |

| 2.4.1 EIT Principle and Mathematical Model        |    |

| 2.4.2 Hardware Components in EIT                  |    |

| 2.4.2.1 EIT System Waveform Generator             |    |

| 2.4.2.2 EIT System Excitation Source              |    |

| 2.4.2.3 EIT Data Acquisition System (DAS)         |    |

|                                                   |    |

| 2.4.2.4 EIT Phantom System                        |    |

| 2.4.3 Image Reconstruction in EIT                 | 42 |

| 2.4.3.1 Current Drive Pattern in EIT              | 43 |

| 2.4.3.2 Finite Element Method in EIT              | 44 |

| 2.4.3.3 Reconstruction Algorithms in EIT          | 45 |

| 2.5 Key Progress and Challenges in EIT            | 47 |

| 2.5.1 Advantages                                  | 47 |

| 2.5.2 Limitations                                 | 49 |

| 2.5.3 Improvement opportunities                   | 51 |

| 2.6 Proposed Techniques                           | 52 |

| 2.7 Summary                                       | 54 |

| Chapter 2                                         | 55 |

|   | 3.1 Introduction                                          | 55 |

|---|-----------------------------------------------------------|----|

|   | 3.2 EIT System Measurement Method                         | 56 |

|   | 3.2.1 Applied Potential Tomography (APT)                  | 57 |

|   | 3.2.2 Applied Current Tomography (ACT)                    | 57 |

|   | 3.2.3 Voltage Excitation                                  | 58 |

|   | 3.3 Consideration of EIT Excitation subsystem             | 58 |

|   | 3.3.1 Excitation Signal Safety Limit                      | 59 |

|   | 3.3.2 Multi-Frequency Measurement EIT System              | 60 |

|   | 3.3.3 Current Source Benefit and Limitations              | 60 |

|   | 3.3.4 Voltage Source Benefit and Limitations              | 62 |

|   | 3.4 Existing EIT Systems                                  | 63 |

|   | 3.4.1 Existing Design Based on Current Source             | 64 |

|   | 3.4.1.1 Sheffield EIT System                              | 64 |

|   | 3.4.1.2 Kyung Hee Korean EIT System                       | 65 |

|   | 3.4.1.3 Russian Academy EIT System                        | 66 |

|   | 3.4.1.4 University College of London (UCL) EIT System     | 68 |

|   | 3.4.2 Existing Design Based on Voltage Source             | 70 |

|   | 3.4.2.1 Dartmouth College EIT System                      | 71 |

|   | 3.4.2.2 Rensselaer Polytechnic Institute (RPI) EIT System |    |

|   | 3.4.2.3 Kyung Hee University EIT System                   |    |

|   | 3.4.2.4 Trans-Scan TS2000 System                          | 79 |

|   | 3.5 Sussex EIT System                                     | 79 |

|   | 3.6 Summary                                               | 86 |

| C | Chapter 4                                                 | 87 |

|   | 4.1 Introduction                                          | 87 |

|   | 4.2 Voltage Controlled Current Source                     | 89 |

|   | 4.2.1 Enhanced Howland Current Source (EHCS) Circuit      | 91 |

|   | 4.3 Generalized Impedance Converter                       | 94 |

|   | 4.4 Circuit Simulation Results                            |    |

|   |                                                           |    |

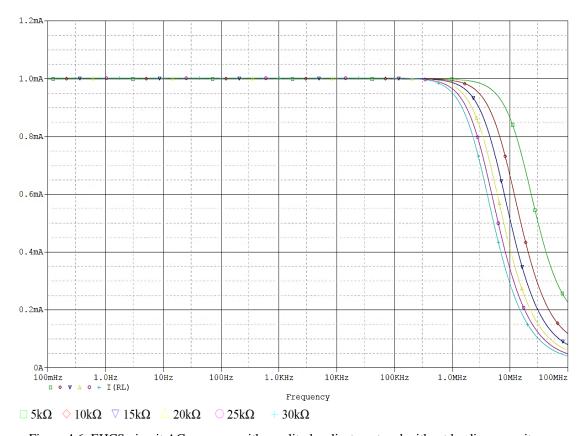

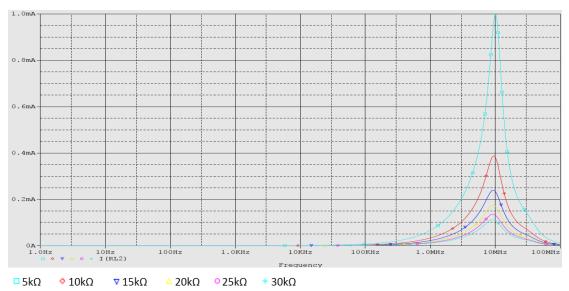

|   | 4.4.1 EHCS Circuit Performance                                        | 99  |

|---|-----------------------------------------------------------------------|-----|

|   | 4.4.1.1 AC Response of the EHCS Circuit                               | 99  |

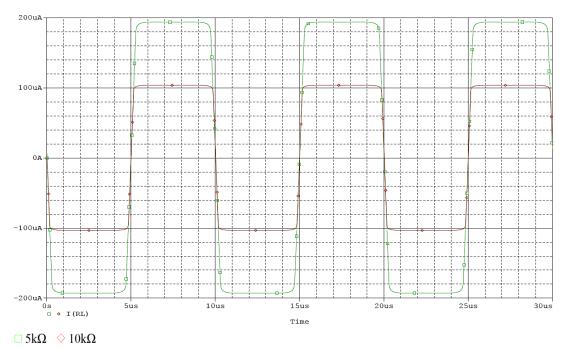

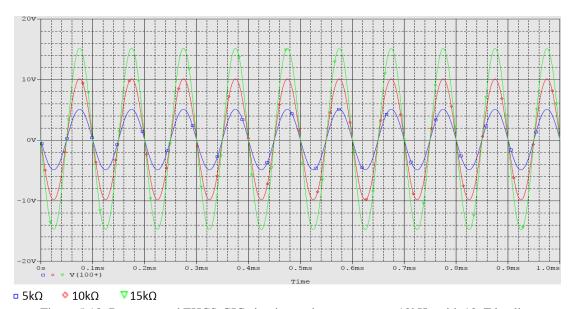

|   | 4.4.1.2 Transient Response of the EHCS Circuit                        | 101 |

|   | 4.4.1.3 Bandwidth and Output Impedance of the EHCS Circuit            | 102 |

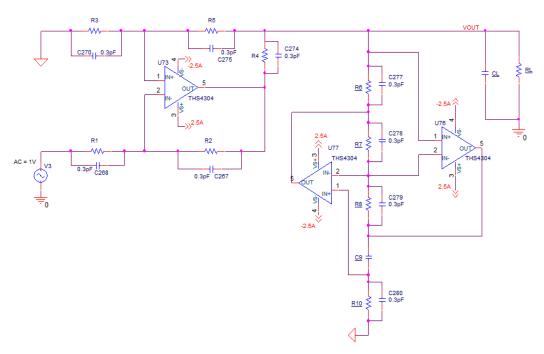

|   | 4.4.2 EHCS with GIC Circuit Performance                               | 103 |

|   | 4.4.2.1 AC Response of the EHCS-GIC Circuit                           | 104 |

|   | 4.4.2.2 Transient Response of the EHCS-GIC Circuit                    | 107 |

|   | 4.4.2.3 Bandwidth and Output Impedance of EHCS-GIC Circuit            |     |

|   | 4.5 Summary                                                           | 109 |

| C | Chapter 5                                                             | 111 |

|   | 5.1 Introduction                                                      | 111 |

|   | 5.2 Bootstrapping Technique                                           | 112 |

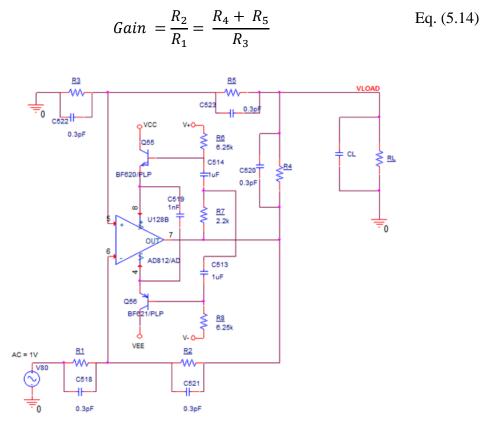

|   | 5.3 Bipolar Current Source                                            | 117 |

|   | 5.4 Guard Amplifier (GA) Technique                                    | 119 |

|   | 5.5 Current Source Circuit Simulation Result                          | 124 |

|   | 5.5.1 Bootstrapped EHCS Performance                                   | 125 |

|   | 5.5.2 Bootstrapped EHCS with GIC Performance                          | 127 |

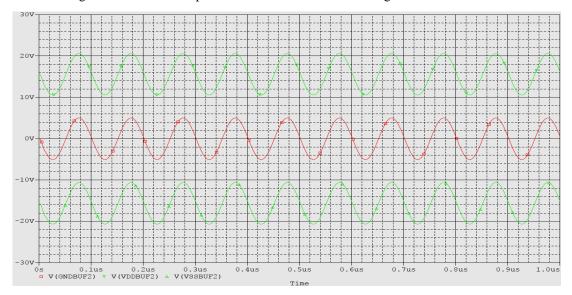

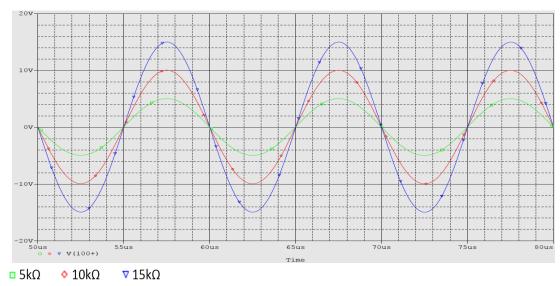

|   | 5.5.2.1 AC Response of Bootstrapped EHCS-GIC Circuit                  | 128 |

|   | 5.5.2.2 Transient Response of Bootstrapped EHCS-GIC Circuit           | 131 |

|   | 5.5.2.3 Bandwidth and Output Impedance of Bootstrapped EHCS-GIC Circ  |     |

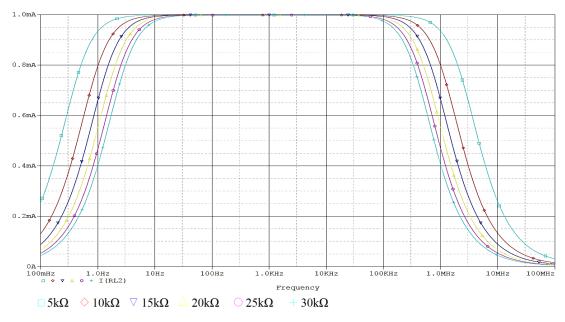

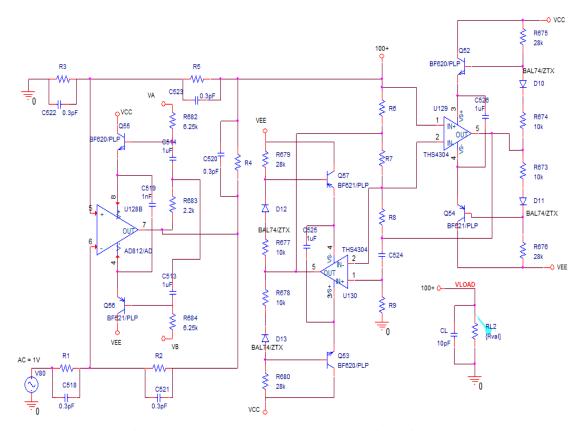

|   | 5.5.3 Bipolar Bootstrapped EHCS-GIC Current Source                    |     |

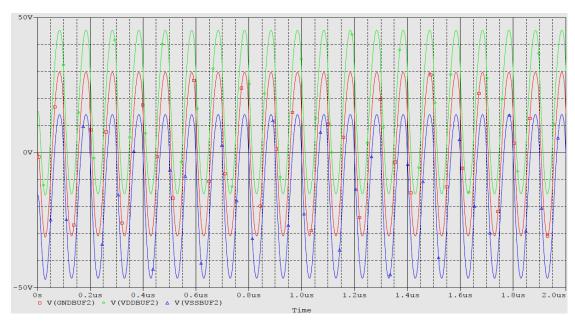

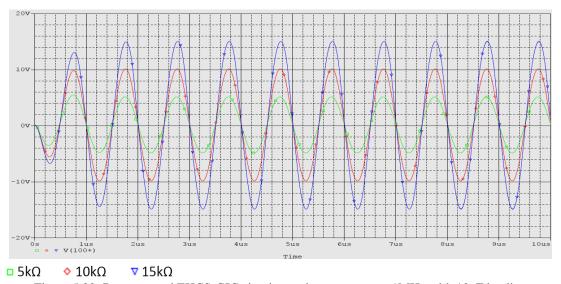

|   | 5.5.3.1 AC Response of Bipolar Bootstrapped EHCS-GIC Circuit          |     |

|   | 5.5.3.2 Transient Response of Bipolar Bootstrapped EHCS-GIC Circuit   |     |

|   | 5.5.3.3 Bandwidth and Output Impedance of Bipolar Bootstrapped EHCS-C | GIC |

|   | Circuit                                                               |     |

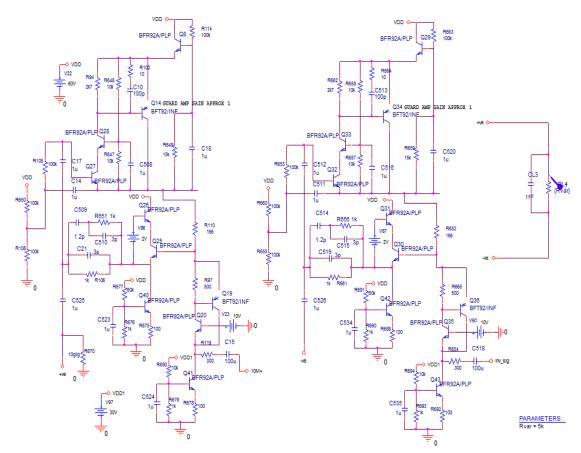

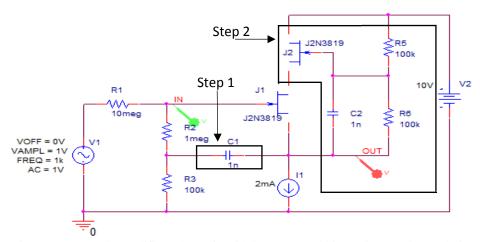

|   | 5.6 High Frequency Discrete Component Current Source (DCCS)           |     |

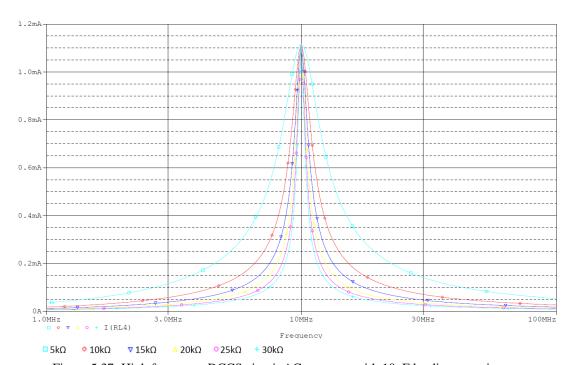

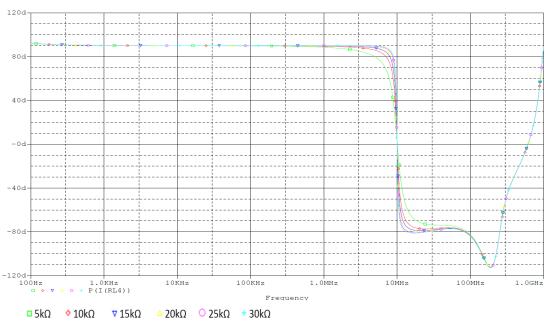

|   | 5.6.1 AC Response of DCCS Circuit                                     | 150 |

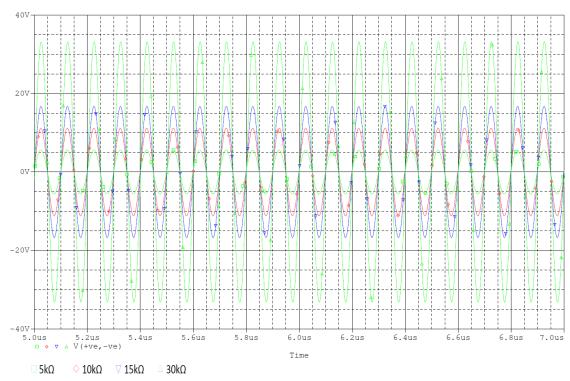

|   | 5.6.2 Transient Response of DCCS Circuit                              | 152 |

|   | 5.6.3 Bandwidth and Output Impedance of DCCS Circuit                  | 153 |

|   | 5.7 Summary                                                           | 154 |

| Chapter 6                                                                                                                                                                                                                                           | 156               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 6.1 Introduction                                                                                                                                                                                                                                    | 156               |

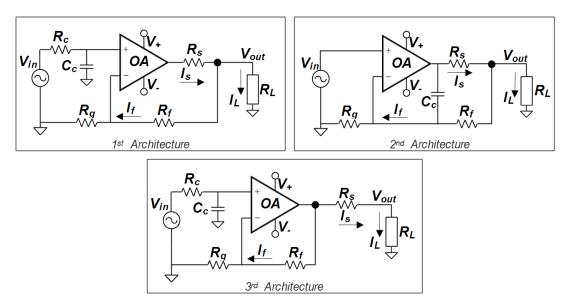

| 6.2 Voltage Source Architecture                                                                                                                                                                                                                     | 158               |

| 6.3 Differential Amplifier Design for Voltage Measurement                                                                                                                                                                                           | 162               |

| 6.4 Voltage Source Circuit Simulation Results                                                                                                                                                                                                       | 173               |

| 6.4.1 Bipolar Bootstrapped Voltage Source Performance                                                                                                                                                                                               | 177               |

| <ul><li>6.4.1.1 AC Response of Bipolar Bootstrapped Voltage Source Circuit</li><li>6.4.1.2 Transient Response of Bipolar Bootstrapped Voltage Source Circu</li><li>6.4.1.3 Performance Parameter of Bipolar Bootstrapped Voltage Source C</li></ul> | iit181<br>Circuit |

| 6.5 Summary                                                                                                                                                                                                                                         |                   |

| Chapter 7                                                                                                                                                                                                                                           | 190               |

| 7.1 Introduction                                                                                                                                                                                                                                    | 190               |

| 7.2 Block Diagram for the Excitation Source Board                                                                                                                                                                                                   | 191               |

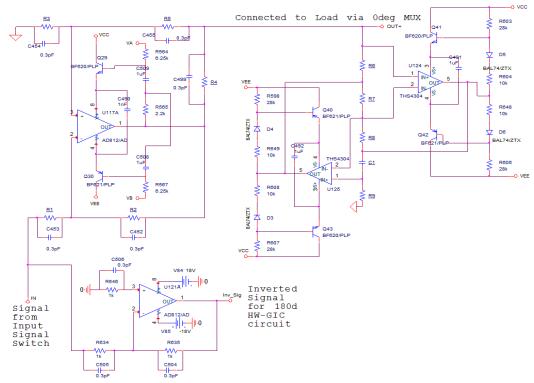

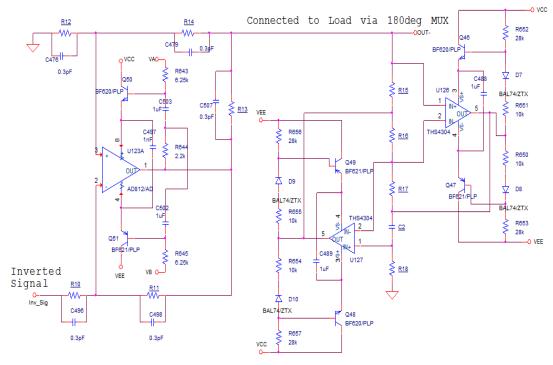

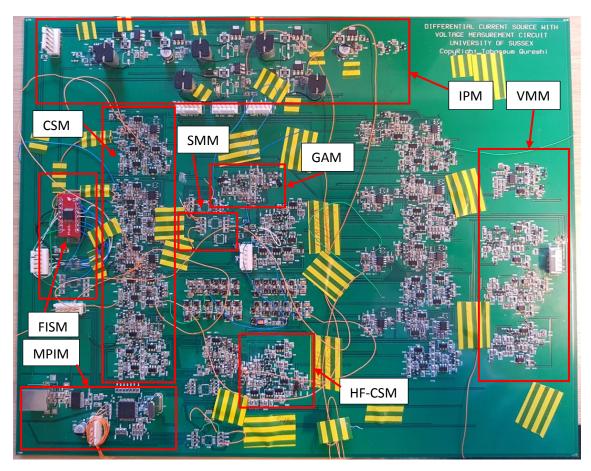

| 7.2.1 Current Source Board (CSB)                                                                                                                                                                                                                    | 191               |

| 7.2.2 Voltage Source Board (VSB)                                                                                                                                                                                                                    | 194               |

| 7.3 Voltage Source PCB Board Performance                                                                                                                                                                                                            | 196               |

| 7.3.1 Voltage Source (VS) Circuit Performance                                                                                                                                                                                                       | 198               |

| 7.3.1.1 Maximum Operational Frequency Test                                                                                                                                                                                                          |                   |

| 7.3.1.3 Phase Difference Test                                                                                                                                                                                                                       | 203               |

| 7.3.1.4 Circuit Maximum Loading Test                                                                                                                                                                                                                |                   |

| 7.3.1.5 SNR Test                                                                                                                                                                                                                                    |                   |

| 7.4 Current Source PCB Board Performance                                                                                                                                                                                                            |                   |

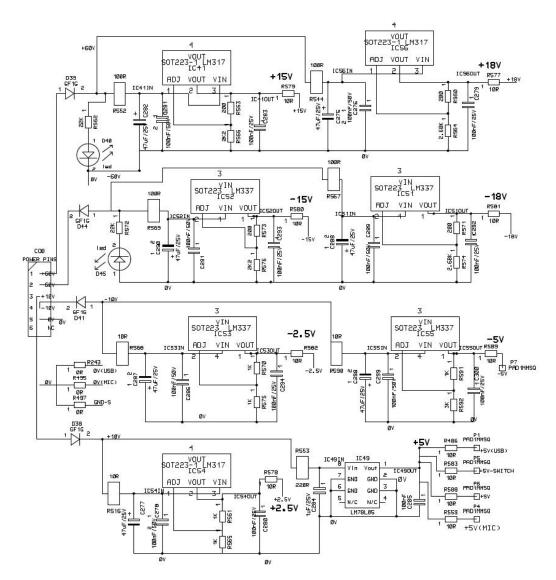

| 7.4.1 Internal Power Module of the CSB                                                                                                                                                                                                              | 213               |

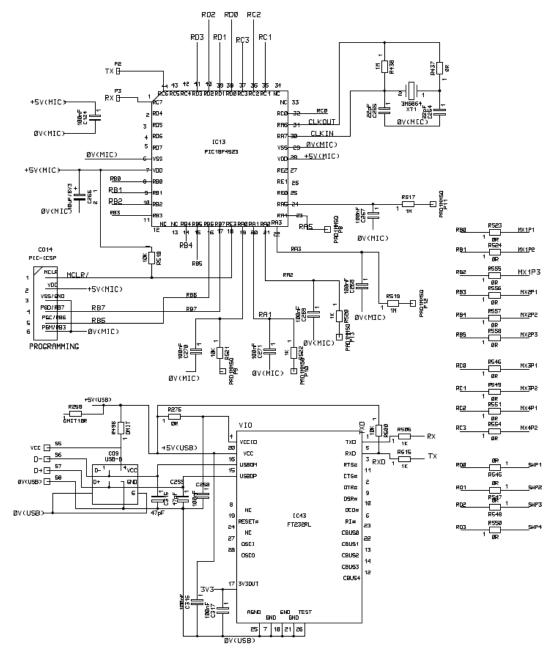

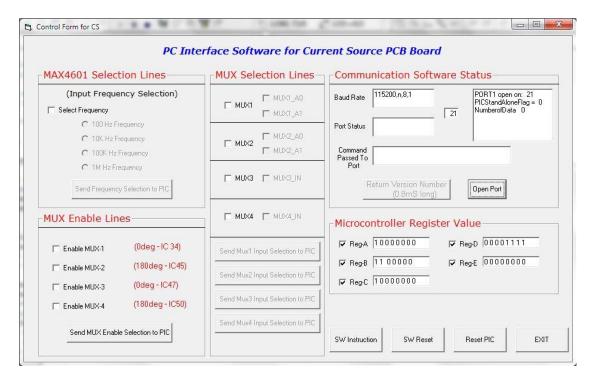

| 7.4.2 Microcontroller & USB Interface of the CSB                                                                                                                                                                                                    | 215               |

| 7.4.3 Current Source Circuit Performance                                                                                                                                                                                                            | 217               |

| 7.4.3.1 Maximum Operational Frequency and Phase Difference Test                                                                                                                                                                                     | 220               |

| 7.4.3.2 Output and Input Impedance Test                                                                                                                                                                                                             | 221               |

| 7.4.3.3 Maximum Loading Test                     | 223 |

|--------------------------------------------------|-----|

| 7.4.4 Guard Amplifier Circuit Performance        | 224 |

| 7.4.5 Differential Amplifier Circuit Performance | 227 |

| 7.5 Summary                                      | 229 |

| Chapter 8                                        | 231 |

| 8.1 Thesis Review                                | 231 |

| 8.2 Thesis Conclusion                            | 235 |

| 8.3 Future Work                                  | 243 |

| Bibliography                                     | 246 |

| Appendices                                       | 260 |

| A: HCS Circuit Analysis                          | 260 |

| B: EHCS Circuit Analysis                         | 263 |

| C: GIC Circuit Analysis                          | 265 |

| D: Guard Amplifier Circuit Testing               | 267 |

| E: VSM Circuit Performance                       | 269 |

| F: Microcontroller Ports Configuration           | 273 |

| G: CSM Circuit Performance                       | 274 |

| H: GAM Circuit Performance                       | 278 |

#### List of Publications

- 1. **Qureshi, T. R.,** Chatwin, C., & Wang, W. (2013), Bio-impedance Excitation system: A comparison of voltage source and current source designs. *APCBEE Procedia*, 7, pp42–47.

- Qureshi, T. R., Chatwin, C. R., Zhou, Z., Li, N. & Wang, W. (2012), Investigation of voltage source design's for electrical impedance mammography (EIM) systems. 34<sup>th</sup> Annual International Conference of the IEEE Engineering in Medicine and Biology Society, pp1582–1585.

- 3. **Qureshi, T. R.,** Chatwin, C. R. & Wang, W. (2012), Design of Wideband Voltage Source Having Low Output Impedance, Flexible Gain and Controllable Feedback Current for EIT Systems. *International proceedings of chemical, biological and environmental engineering (IPCBEE)*, 34, pp45–50.

- Qureshi, T., Mehboob, B., Chatwin, C. R. & Wang, W. (2012), Optimal device for a low output impedance voltage source for electrical Impedance tomography (EIT) systems. *IEEE International Conference on Electro/Information Technology*, pp1–6.

- Qureshi, T. R., Mehboob, B., Chatwin, C. R. & Wang, W. (2012), Wideband voltage source design for EIT systems. 38<sup>th</sup> Annual Northeast Bioengineering Conference (NEBEC), pp353–354.

- Qureshi, T. R., Chatwin, C. R., Huber, N., Zarafshani, A., Tunstall, B. & Wang, W. (2010), Comparison of Howland and general Impedance converter (GIC) circuit based current sources for bio-impedance measurements. *Journal of Physics: Conference Series*, 224, p012167.

- Qureshi, T. R., Li, N., Zarafshani, A., Béqo, N., Chatwin, C. R. & Wang, W. (2012), Performance comparison between voltage source design and current source for Electrical Impedance Mammography (EIM) systems, 13<sup>th</sup> International Conference on Biomedical Applications of EIT, 23-25 May, Tianjin China (Accepted for Presentation).

- 8. Zarafshani, A., **Qureshi, T.,** Bach, T., Chatwin, C. R. & Soleimani, M. (2016), A 3D multi-frequency response electrical mesh phantom for validation of the planar

- structure EIT system performance. *IEEE International Conference on Electro Information Technology (EIT)*, pp0600–0604.

- 9. Zarafshani, A., **Qureshi, T. R.,** Bach, T., Chatwin, C. & Soleimani, M. (2016), An Electronic Mesh phantom for planar structure EIT systems *16<sup>th</sup> International Conference on Electrical Bio-impedance (ICEBI) and 17<sup>th</sup> Conference on Biomedical Applications of Electrical Impedance Tomography (EIT), 19-23 June, Stockholm, Sweden, (Accepted for Presentation).*

- 10. Zhang, X., **Qureshi, T.,** Chatwin, C. & Wang, W. (2014), Validity of Using the Sheffield Algorithm for the Sussex EIT MK4, 15<sup>th</sup> International Conference on Biomedical Applications of Electrical Impedance Tomography, Canada, p68.

- 11. Beqo, N., Zarafshani, A., **Qureshi, T. R.,** Chatwin, C., Wang, W., (2013), Converting EIT voxel based imaging and pixel based ultrasound imaging to standardised DICOM, *XV*<sup>th</sup> *International Conference on Electrical Bio-Impedance (ICEBI) and XIV*<sup>th</sup> *Conference on Electrical Impedance Tomography* (*EIT*), 22–25 April, Heilbad Heiligenstadt, Germany (Poster Presentation).

- 12. Zarafshani, A., Hashemi, H., Beqo, N., Chatwin, C., Wang, W. & **Qureshi, T. R.** (2013), Multi-frequency response mesh phantom for validation of EIT system performance, *XVth International Conference on Electrical Bio-Impedance (ICEBI) and XIV<sup>th</sup> Conference on Electrical Impedance Tomography (EIT)*, 22–25 April, Heilbad Heiligenstadt, Germany (Poster Presentation).

- Li, N., Qureshi, T. R., Zarafshani, A., Béqo, N., Zhou, Z., Xu, H., Chatwin, C.

R. & Wang, W. (2012), Fast Lock-in System for Biological Cell Impedance Analysis 13<sup>th</sup> International Conference on Biomedical Applications of EIT, 23-25 May, Tianjin China (Accepted for Presentation).

### List of Acronyms

2D: Two-dimensional3D: Three-dimensionalAC: Alternating current

ACT: Applied Current Tomography

ADC: Analogue-to-digital converter

APT: Applied Potential Tomography

BI: Bio-Impedance

BIM: Bio-impedance Measurement

BIS Bio-Impedance Spectroscopy

CAT/CT: Computerized axial tomography

CMMR: Common-mode rejection Ratio

CMOS: Complementary metal–oxide–semiconductor

CS: Current Source

CSB: Current Source Board

CSM: Current Source Module

DA: Differential Amplifier

DAC: Digital-to-analogue convertor DAS: Data Acquisition System

DC: Direct Current

DCCS: Discrete Component Current Source

DCIS: Ductal Carcinoma in-situ

DDS: Direct Digital Synthesizer

DSP: Digital signal processor

DV: Differential Voltage

EHCS: Enhanced Howland Current Source

EIDORS: EIT and Diffuse Optical Tomography Reconstruction Software

EIM: Electrical Impedance Mammography

EIS: Electrical Impedance Spectroscopy

EIT: Electrical Impedance Tomography

ERT: Electrical Resistance tomography

ESM: Electrode Support Module FDM: Finite Difference Method FEM: Finite Element Method FFT: Fast Fourier Transform FG: Function Generator

FISM: Front-end Input Switching Module FPGA: Field programmable gate array

GA: Guard Amplifier

GAM: Guard Amplifier Module GBP: Gain Bandwidth Product

GIC: Generalized Impedance Convertor

HCS: Howland current source

HCSC: Howland current source circuit

HF-CSM: High Frequency-Current Source Module

IA: Instrumentation amplifier

IC: Integrated Circuit

IDC: Invasive Ductal CarcinomaILC: Invasive Lobular CarcinomaIMM: Impedance Measurement Module

IPM: Internal Power Module

LCIS: Lobular Carcinoma in-situ

LM: Load Module LPF: Low-pass filter

MF-EIT: Multi-frequency EIT

MPIM: Microcontroller and PC Interface Module

MRI: Magnetic resonance imaging

MUX: Multiplexer

NCO: Numerical controlled oscillator

NI: National Instruments

NIC: Negative Impedance Converter

OTA: Operational trans-conductance amplifier

PCB: Printed Circuit Board PET: Positron imaging test

PROM: Programmable read-only memory PSD: Phase-sensitive demodulation

RC: Resistor-Capacitor RMS: Root mean Square

SMC: Surface mount component SMD: Surface-Mount Device

SMM: Signal Multiplexing Module

SNR: Signal-to-noise ratio

SUO: Sample under observation

TAM: Trans-admittance Mammography

THC: Through-hole component

VCCS: Voltage Controlled Current Source VCVS: Voltage Controlled Voltage Source

V-I: Voltage-to-Current Converter VMM: Voltage Measurement Module

VS: Voltage source

VSB: Voltage Source Board VSM: Voltage Source Module

## List of Symbols

%: Percentage MHz: Mega-Hertz <: Less than mm: Millimetre

>: Greater than mm<sup>2</sup>: Square millimetre

±: Positive and Negative polarity mm<sup>3</sup>: Cubic millimetre

Δ: Delta mS: Milli-siemens

||: Parallel combination mW: Milli-watt

$\approx$ : Approximate M $\Omega$ : Mega-ohm

≤: Less than and equal to nA: Nano-ampere

≥: Greater than and equal to nF: Nano-farad

ω: Angular frequency °: Degree

μA: Microampere pC: Pico-coulombs

us: Microsecond pF: Pico-farad

∞: Infinity p-p: Peak-to-peak

cm: Centimetre s: Seconds

dB: Decibel s<sup>-1</sup>: Per Second

F: Farad tpc: Times per cycle

fc: Relaxation frequency V: Voltage and Volts

fps: Frames per second Z: Impedance

G $\Omega$ : Giga ohm  $\alpha$ : Relaxation factor constant

Hz: Hertz  $\varepsilon$ : Permittivity

Current λ: Wavelength

*j*: Complex number σ: Electrical impedance distribution

J: Current density distribution  $\Phi$ : Phase difference

Kilo  $\Omega$ : Ohm

kHz: Kilo-Hertz  $\phi$ : Electrical potential distribution

M: Mega

I:

k:

mA: Milliamp

# List of Figures

| Figure 1.1: Most common cancers incidence in the UK (Cancer Research UK, 2013a) 3                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: a) Localised and invasive DCIS cancer b) Localised and invasive LCIS cancer                                                  |

| (Cancer Research UK, 2016 & 2015a)                                                                                                       |

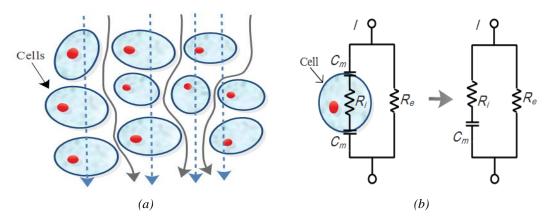

| Figure 2.1: a) Current flow through cells at low (gray line) and high (blue dotted line) frequencies.                                    |

| b) The 3-element equivalent circuit model of biological impedance                                                                        |

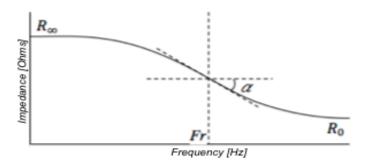

| Figure 2.2: Impedance plot vs Frequency (Beqo, 2012)                                                                                     |

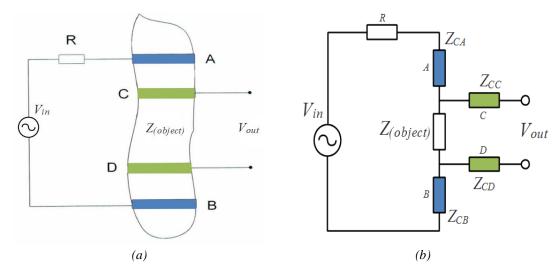

| Figure 2.3: a) The 4-electrode measurement configuration. b) The equivalent 4-electrode                                                  |

| measurement circuit with electrode contact impedance Z <sub>CA</sub> , Z <sub>CB</sub> , Z <sub>CC</sub> & Z <sub>CD</sub> (Yang, 2006). |

|                                                                                                                                          |

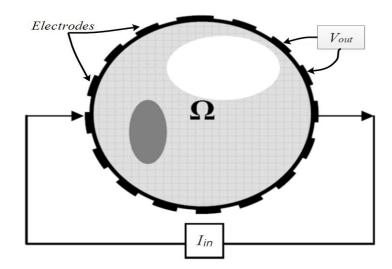

| Figure 2.4: 16-Electrode EIT measurement diagram. Measurement of Voltage (Vout) after                                                    |

| injecting the current $(I_{in})$ into the medium $\Omega$ (Molinari, 2003)                                                               |

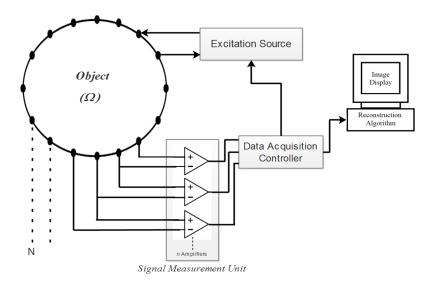

| Figure 2.5: Block Diagram of a typical EIT system                                                                                        |

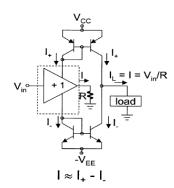

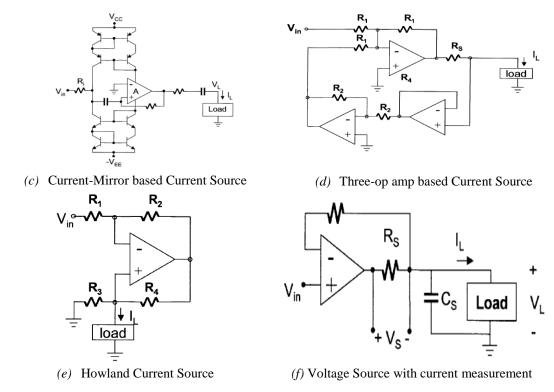

| Figure 2.6: Current and voltage sources reported in the literature for EIT (a-e), and (f) (Holder,                                       |

| 2005)                                                                                                                                    |

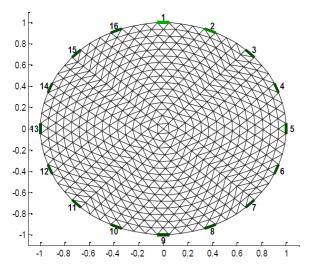

| Figure 2.7: Typical 2D mesh for FEM with 16-electrodes                                                                                   |

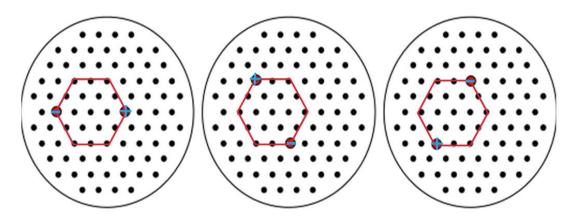

| Figure 3.1: Current injection configuration in a Hexagonal electrode configuration: 0° (left), 120°                                      |

| (middle) and 240° (right). Dots with + & - represents the current drive pairs. Dots in the red                                           |

| hexagonal area represent the voltage measurement electrodes (Sze et al., 2011) 85                                                        |

| Figure 4.1: Norton equivalent of a practical current source                                                                              |

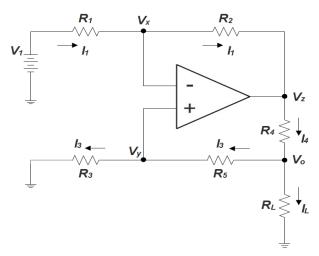

| Figure 4.2: A differential VCCS using Howland circuit                                                                                    |

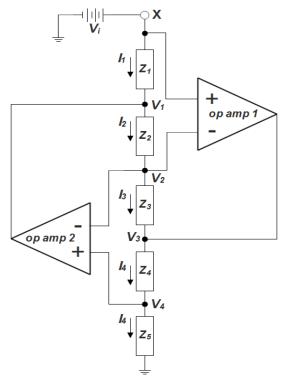

| Figure 4.3: Generalized Impedance Converter circuit                                                                                      |

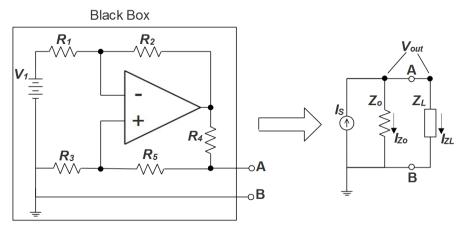

| Figure 4.4: A VCCS and its Norton equivalent circuit                                                                                     |

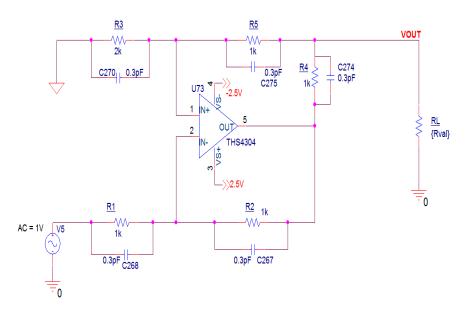

| Figure 4.5: EHCS circuit simulation setup in Orcad-Pspice®                                                                               |

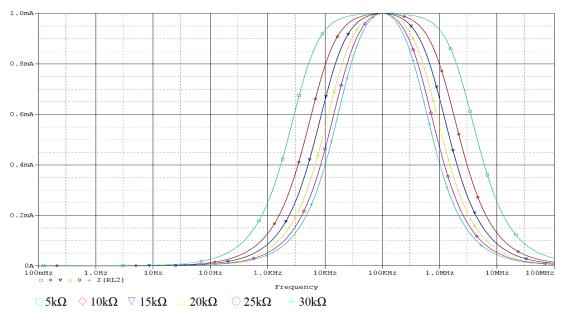

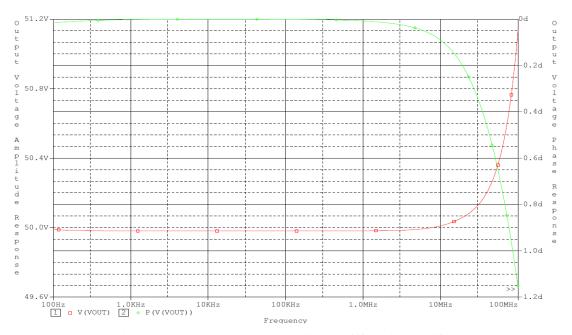

| Figure 4.6: EHCS-circuit AC response with amplitude adjustment and without loading capacitance                                           |

| Figure 4.7: EHCS-circuit transient response at 100kHz without loading capacitance                                                        |

| Figure 4.8: EHCS-GIC circuit simulation setup                                                                                            |

| Figure 4.9: EHCS-GIC circuit Improved AC response for 100Hz –1kHz with 10pF loading capacitance                                          |

| Figure 4.10: EHCS-GIC circuit Improved AC response for 100kHz with 10pF loading                                                          |

| capacitance                                                                                                                              |

| Figure 4.11: EHCS-GIC circuit Improved AC response for 1MHz with 10pF loading capacitance                                                |

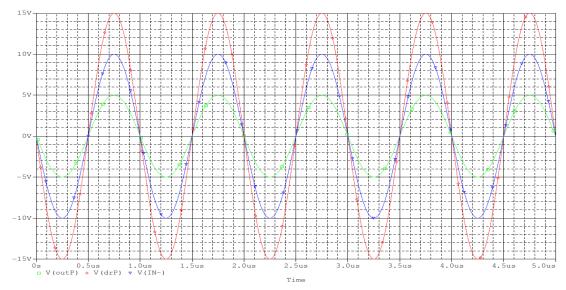

| Figure 4.12: EHCS-GIC circuit transient response at 10kHz with loading capacitance 107                                                   |

| Figure 4.13: FHCS-GIC circuit output impedance with 10kO resistive loading 109                                                           |

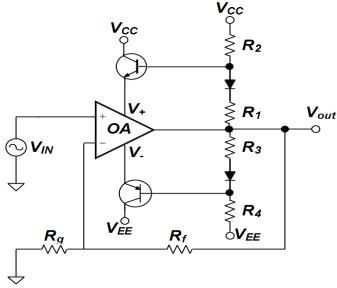

| Figure 5.1: A bootstrapping circuit used in which $V_+$ and $V$ changes as a function of the output |

|-----------------------------------------------------------------------------------------------------|

| voltage                                                                                             |

| Figure 5.2: A bootstrapped circuit simulation providing $\approx 100 V_{p\text{-}p}$                |

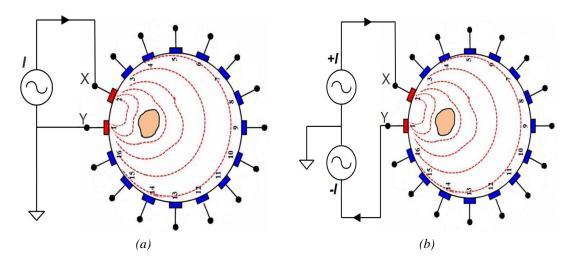

| Figure 5.3: A Current Source injection for EIT system: (a) Single-end (b) Differential 11           |

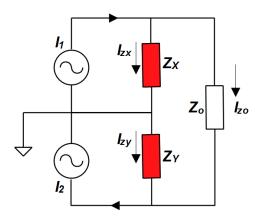

| Figure 5.4: A Differential CS equivalent circuit model                                              |

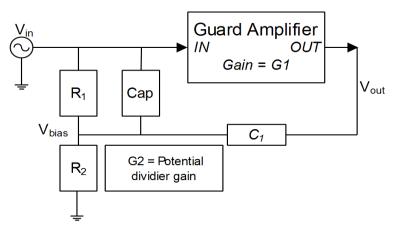

| Figure 5.5: Guard Amplifier block diagram                                                           |

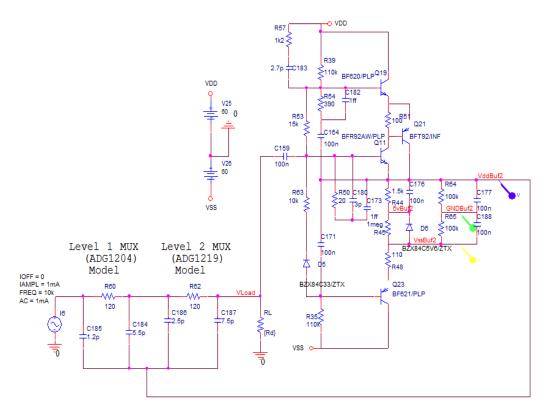

| Figure 5.6: Designed Guard Amplifier for current source circuit                                     |

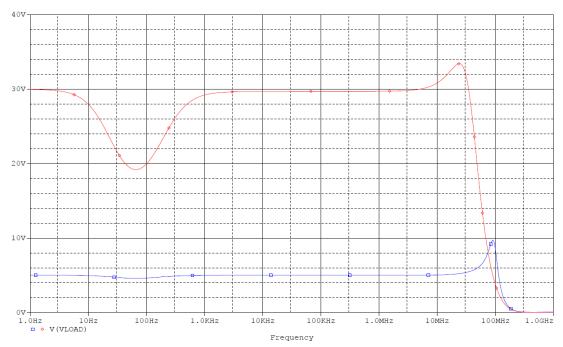

| Figure 5.7: AC response of GA circuit with capacitance cancelation                                  |

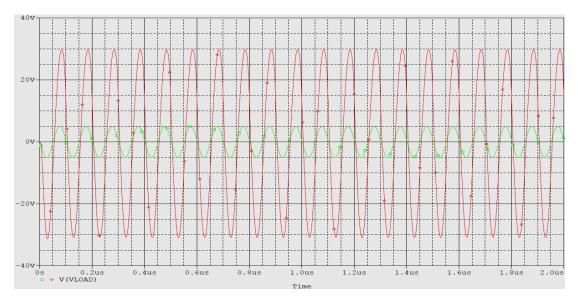

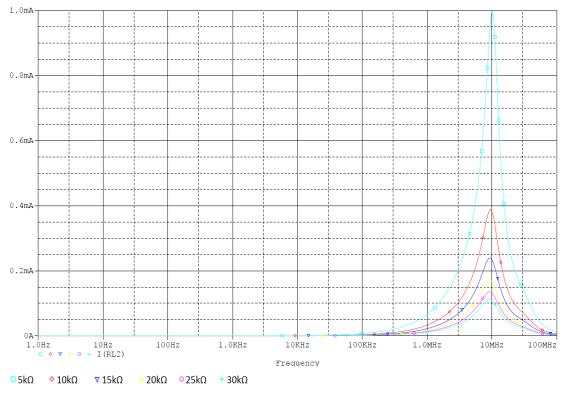

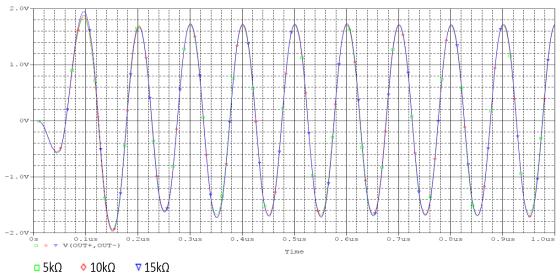

| Figure 5.8:Transient response of GA circuit at $10 MHz$ using $5 k\Omega$ and $30 k\Omega$ Load     |

| Figure 5.9: GA circuit buffered output voltages at $10 MHz$ using $5 k\Omega$ Load                  |

| Figure 5.10: GA circuit buffered output voltages at $10 MHz$ using $30 k\Omega$ Load                |

| Figure 5.11: Bootstrapped EHCS-circuit simulation setup                                             |

| Figure 5.12: Bootstrapped EHCS-GIC circuit simulation setup                                         |

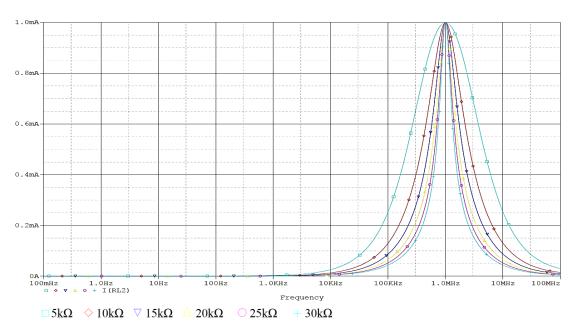

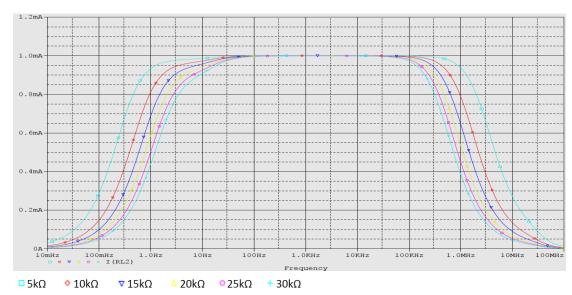

| Figure 5.13: Bootstrapped EHCS-GIC circuit AC response for 0.1-1kHz with 10pF loading               |

| capacitance 129                                                                                     |

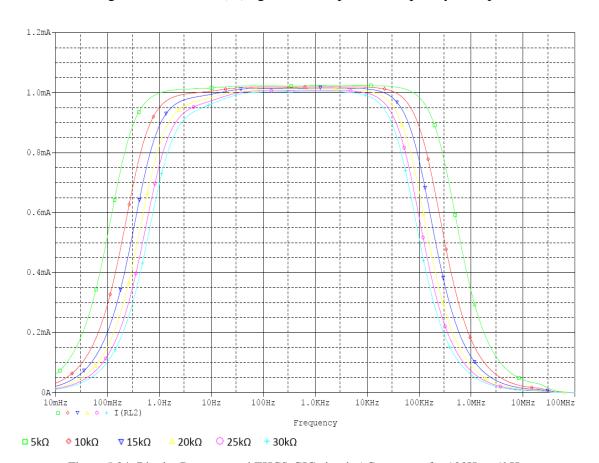

| Figure 5.14: Bootstrapped EHCS-GIC circuit AC response at 10kHz with 10pF loading                   |

| capacitance 12                                                                                      |

| Figure 5.15: Bootstrapped EHCS-GIC circuit AC response at 100kHz with 10pF loading                  |

| capacitance 129                                                                                     |

| Figure 5.16: Bootstrapped EHCS-GIC circuit AC response at 1MHz with 10pF loading                    |

| capacitance 130                                                                                     |

| Figure 5.17: Bootstrapped EHCS-GIC circuit AC response at 10MHz with 10pF loading                   |

| capacitance 130                                                                                     |

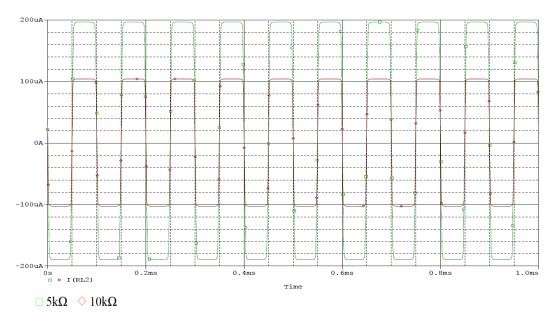

| Figure 5.18: Bootstrapped EHCS-GIC circuit transient response at 10kHz with 10pF loading            |

| capacitance 13                                                                                      |

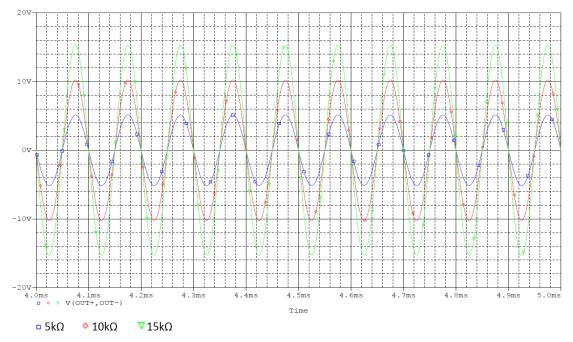

| Figure 5.19: Bootstrapped EHCS-GIC circuit transient response at 100kHz with 10pF loading           |

| capacitance 13                                                                                      |

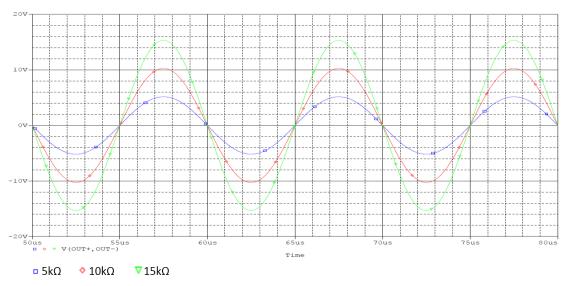

| Figure 5.20: Bootstrapped EHCS-GIC circuit transient response at 1MHz with 10pF loading             |

| capacitance 13                                                                                      |

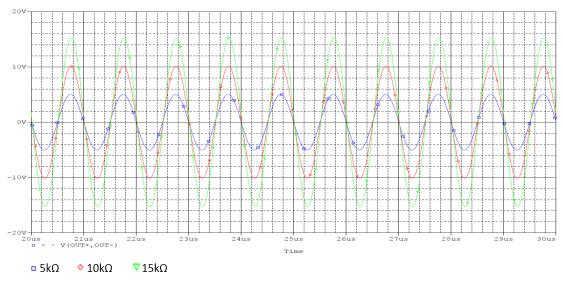

| Figure 5.21: Bootstrapped EHCS-GIC circuit transient response at 10MHz with 10pF loading            |

| capacitance 13:                                                                                     |

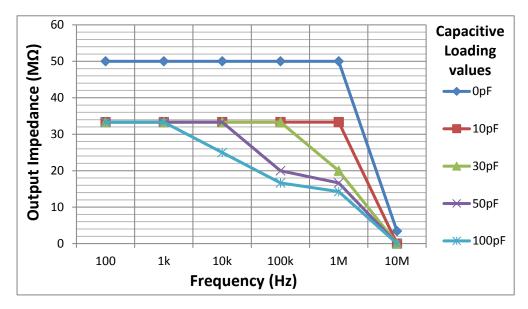

| Figure 5.22: Bootstrapped EHCS-GIC circuit output Impedance with $10k\Omega$ resistive loading 130  |

| Figure 5.23: Bipolar Bootstrapped EHCS-GIC circuit simulation setup                                 |

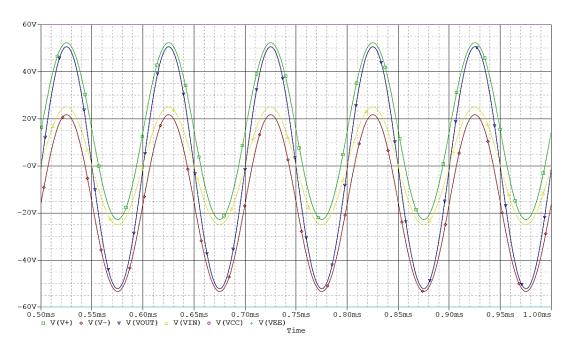

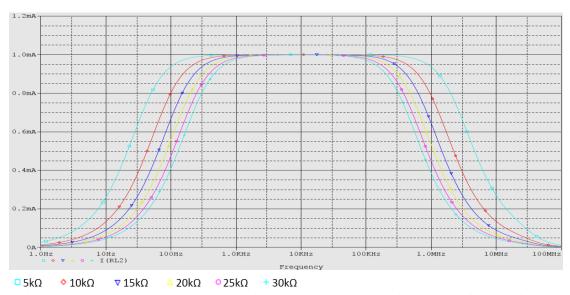

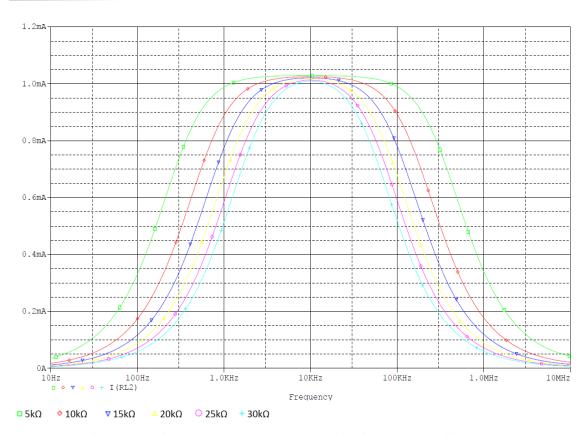

| Figure 5.24: Bipolar Bootstrapped EHCS-GIC circuit AC response for 100Hz – 1kHz 139                 |

| Figure 5.25: Bipolar Bootstrapped EHCS-GIC circuit AC response for 10kHz                            |

| Figure 5.26: Bootstrapped EHCS-GIC circuit AC response for 100kHz with                              |

| Figure 5.27: Bootstrapped EHCS-GIC circuit AC response for IMHz with                          |

|-----------------------------------------------------------------------------------------------|

| Figure 5.28: Bootstrapped EHCS-GIC circuit AC response for 10MHz with                         |

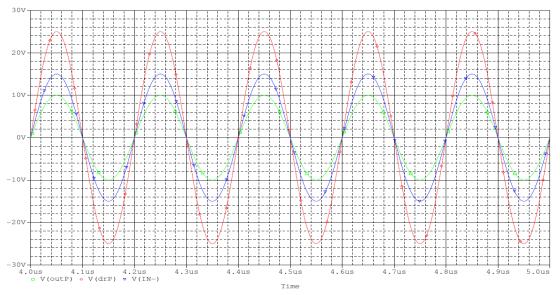

| Figure 5.29: Bipolar bootstrapped EHCS-GIC circuit transient response at 10kHz with 10pH      |

| loading capacitance 142                                                                       |

| Figure 5.30: Bipolar bootstrapped EHCS-GIC circuit transient response at 100kHz with 10pH     |

| loading capacitance 143                                                                       |

| Figure 5.31: Bipolar bootstrapped EHCS-GIC circuit transient response at 1MHz with 10pH       |

| loading capacitance                                                                           |

| Figure 5.32: Bipolar bootstrapped EHCS-GIC circuit transient response at 10MHz with 10pH      |

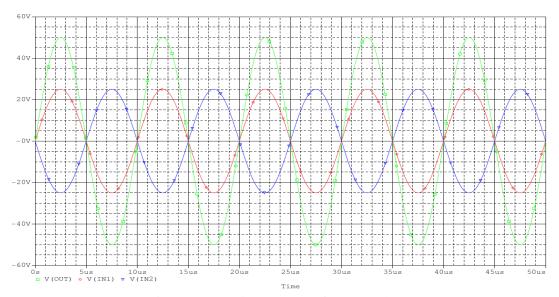

| loading capacitance                                                                           |

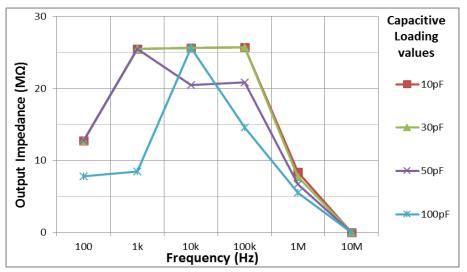

| Figure 5.33: Bipolar bootstrapped EHCS-GIC circuit output impedance with                      |

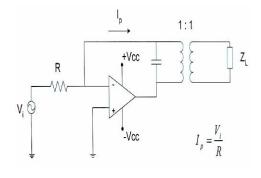

| Figure 5.34: High frequency discrete component source principle                               |

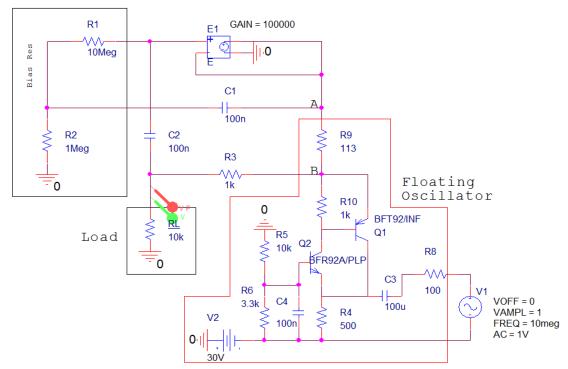

| Figure 5.35: High frequency (10MHz) discrete component source with floating oscillator: Phase |

| Response (top), Load voltage amplitude (bottom)                                               |

| Figure 5.36: High frequency discrete component current source                                 |

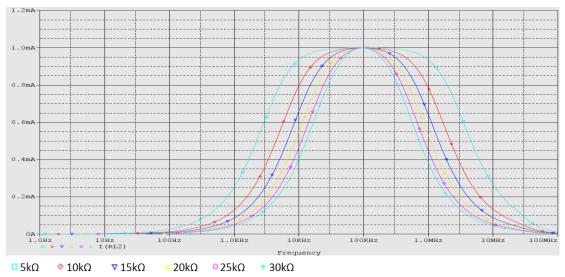

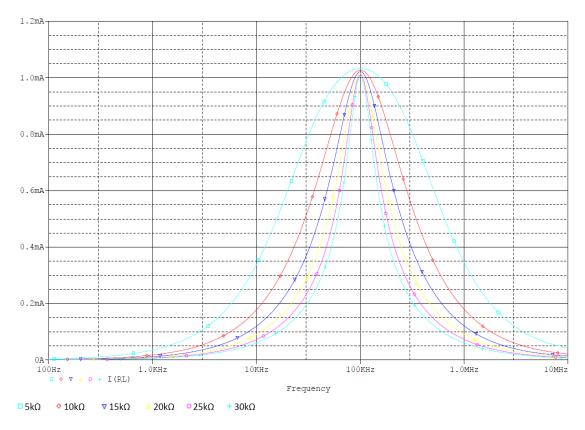

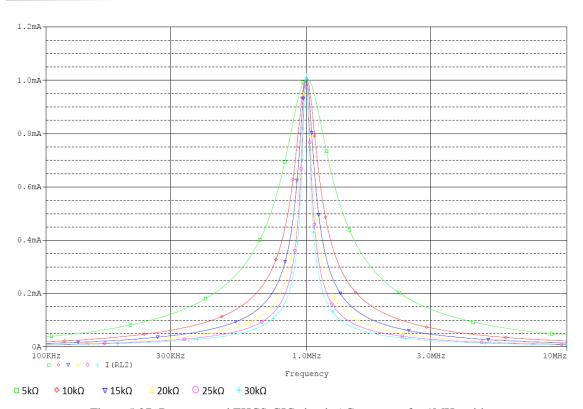

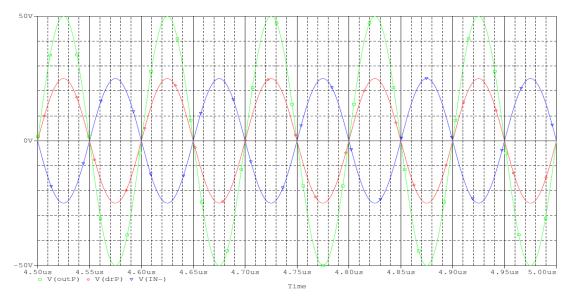

| Figure 5.37: High frequency DCCS circuit AC response with 10pF loading capacitance 151        |

| Figure 5.38: High frequency DCCS circuit phase response with 10pF loading capacitance 152     |

| Figure 5.39: Transient response High frequency CS circuit at 10MHz with 10pF loading          |

| capacitance                                                                                   |

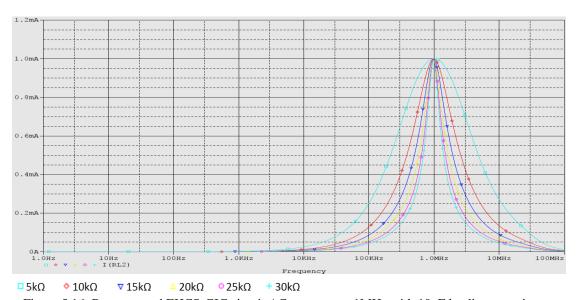

| Figure 5.40: Bipolar DCCS circuit output impedance at 10MHz                                   |

| Figure 6.1: A Single-end voltage source circuit architectures                                 |

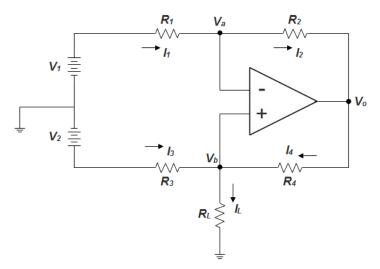

| Figure 6.2: A single op-amp based differential amplifier                                      |

| Figure 6.3: AC response based on differential amplifier using one op-amp                      |

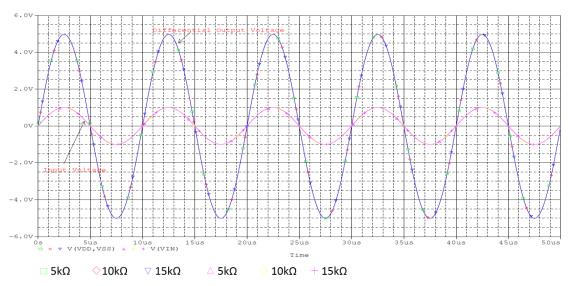

| Figure 6.4: Transient response of DA at 100kHz                                                |

| Figure 6.5: Transient response of DA at 1MHz                                                  |

| Figure 6.6: Transient response of DA at 10MHz                                                 |

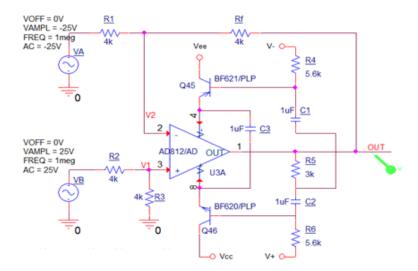

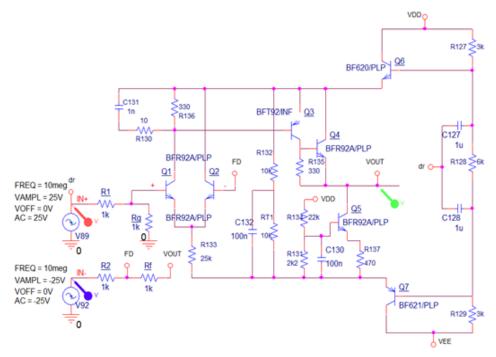

| Figure 6.7: High voltage and high frequency discrete differential amplifier                   |

| Figure 6.8: AC response based on discrete differential amplifier                              |

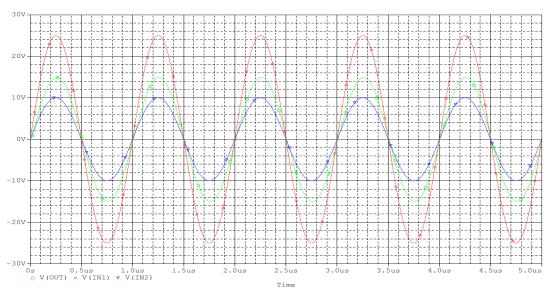

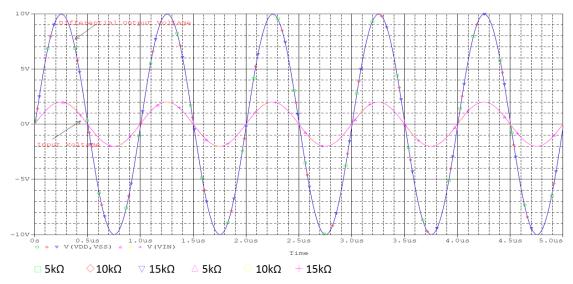

| Figure 6.9: Transient response of discrete DA at 1MHz                                         |

| Figure 6.10: Transient response of discrete DA at 5MHz                                        |

| Figure 6.11: Transient response of discrete DA at 10MHz                                       |

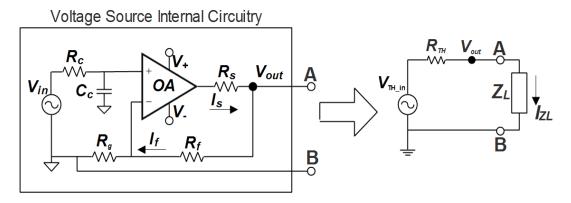

| Figure 6.12: A VCVS and its Thevenin Equivalent circuit                                       |

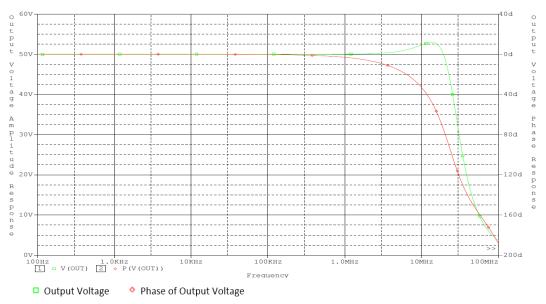

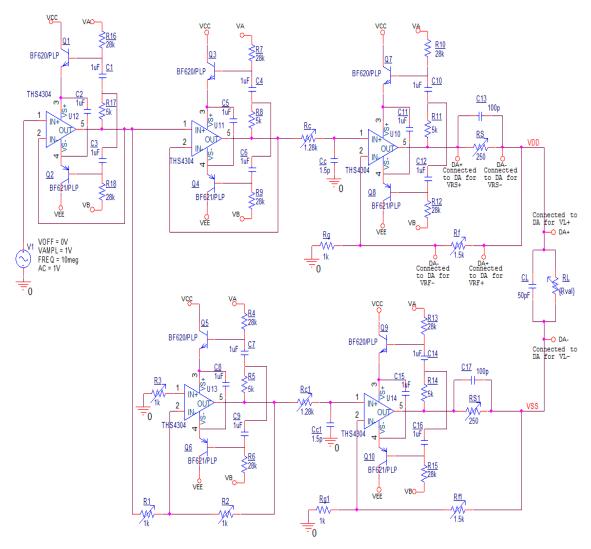

| Figure 6.13: A bipolar bootstrapped voltage source circuit                                    |

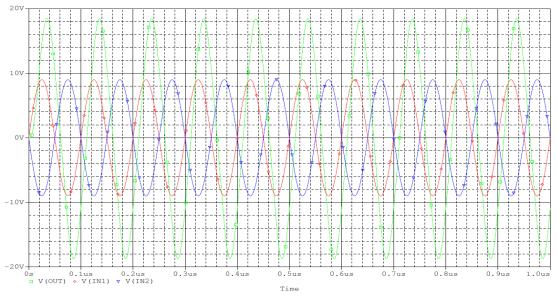

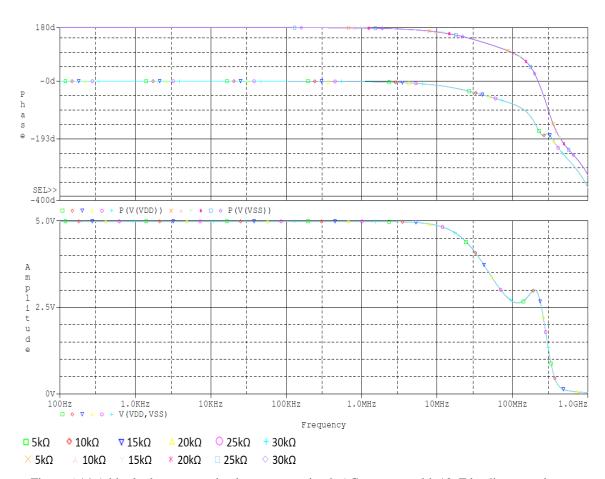

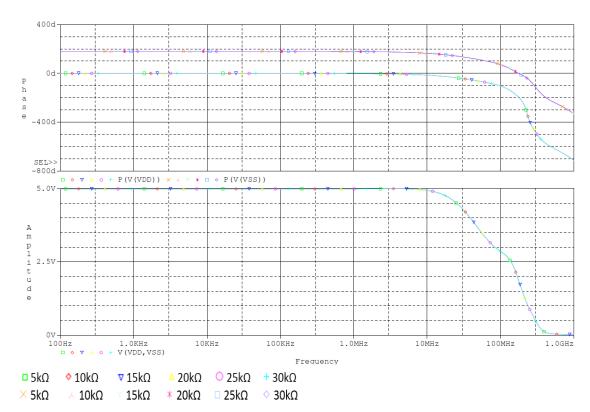

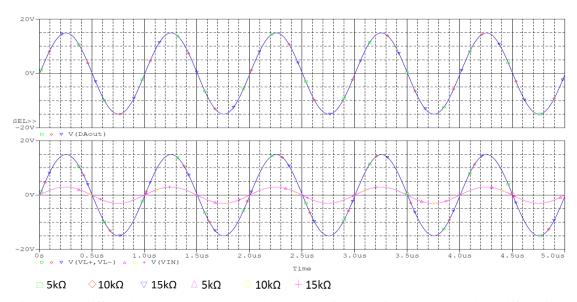

| Figure 6.14:A bipolar bootstrapped voltage source circuit AC response with 10pF loading       |

| capacitance 179                                                                               |

| Figure 6.15: A bipolar bootstrapped voltage source circuit AC response with 50pF loading      |

| capacitance 180                                                                               |

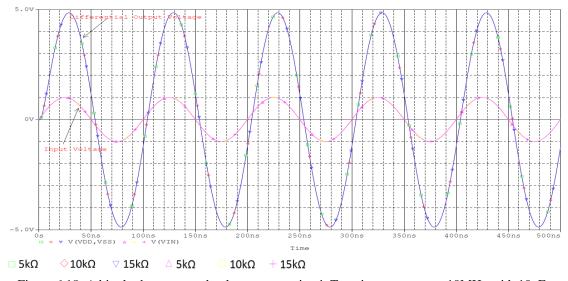

| Figure 6.16: A bipolar bootstrapped voltage source circuit Transient response at 100kHz         | with |

|-------------------------------------------------------------------------------------------------|------|

| 10pF loading capacitance                                                                        | 182  |

| Figure 6.17: A bipolar bootstrapped voltage source circuit Transient response at 1MHz with 1    | 0pF  |

| loading capacitance                                                                             | 182  |

| Figure 6.18: A bipolar bootstrapped voltage source circuit Transient response at 10MHz          | with |

| 10pF loading capacitance                                                                        | 182  |

| Figure 6.19: Differential voltage across load with 10pF loading capacitance: Output u           | sing |

| Differential amplifier (top) & Output using Differential voltage probes (bottom)                | 183  |

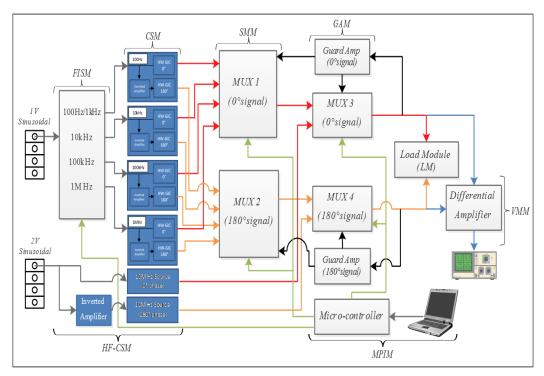

| Figure 7.1: Block Diagram of CSB                                                                | 194  |

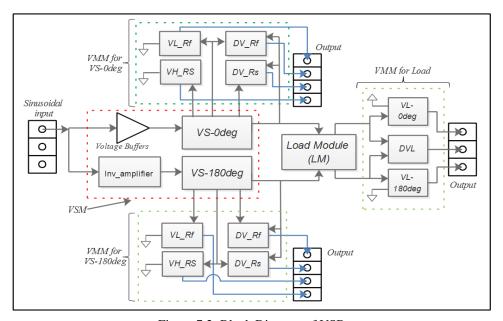

| Figure 7.2: Block Diagram of VSB                                                                | 195  |

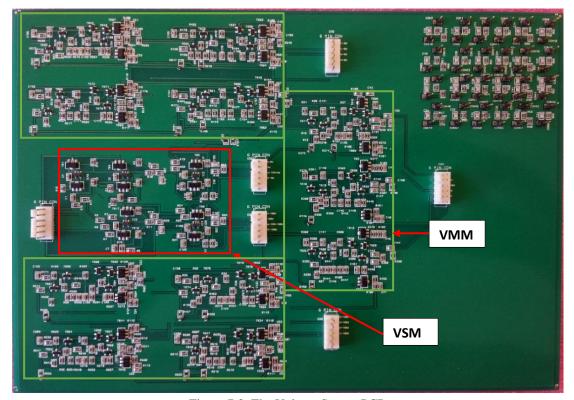

| Figure 7.3: The Voltage Source PCB.                                                             | 197  |

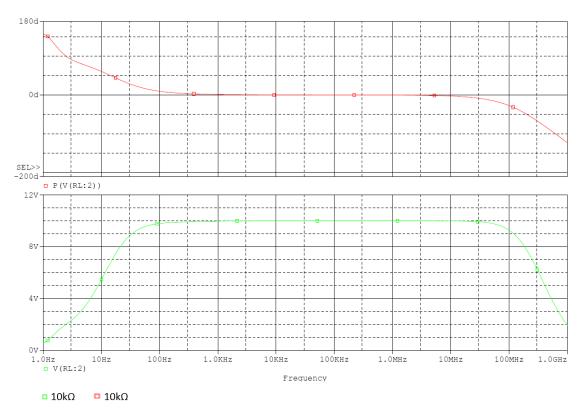

| Figure 7.4: Function Generator operational characteristics                                      | 198  |

| Figure 7.5: MI007 probe characteristics                                                         | 199  |

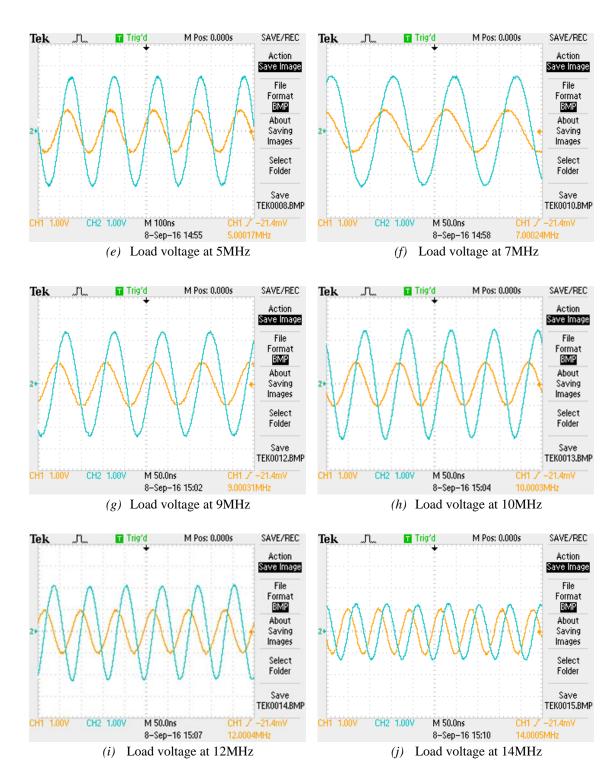

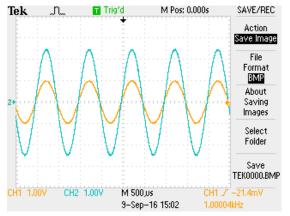

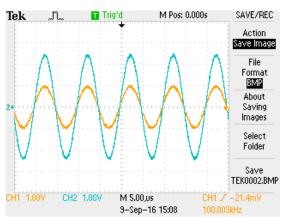

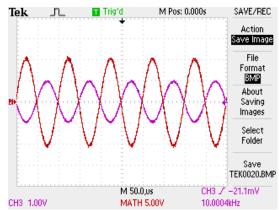

| Figure 7.6: Voltage Source loading voltage at different frequencies                             | 200  |

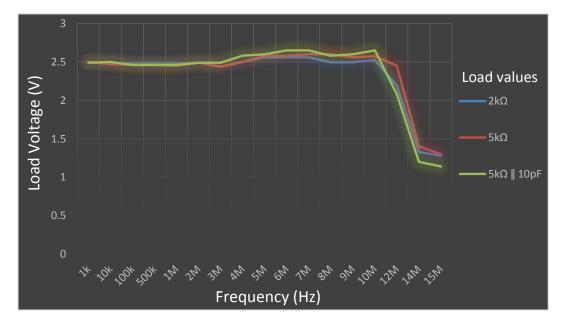

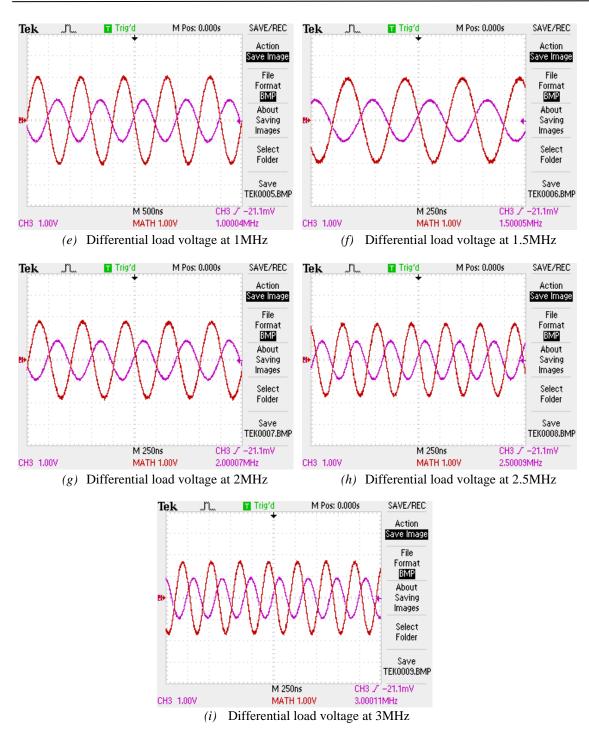

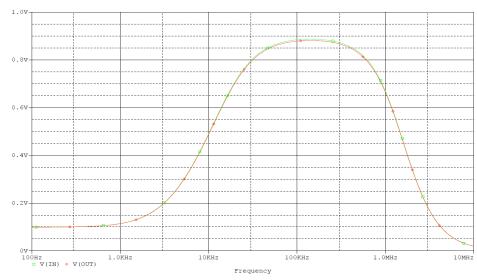

| Figure 7.7: Load voltage versus Frequency                                                       | 201  |

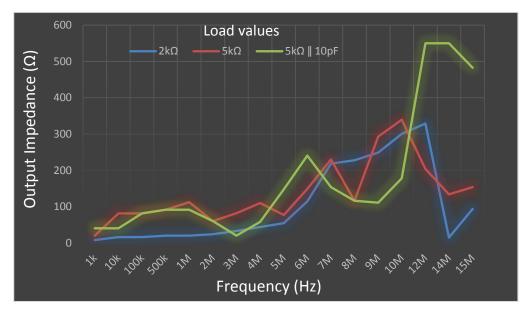

| Figure 7.8: Output impedance versus Frequency                                                   | 202  |

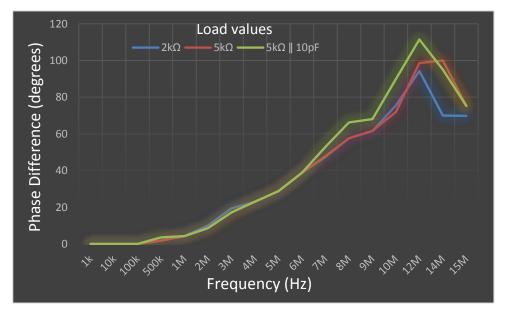

| Figure 7.9: Phase difference plot versus Frequency                                              | 203  |

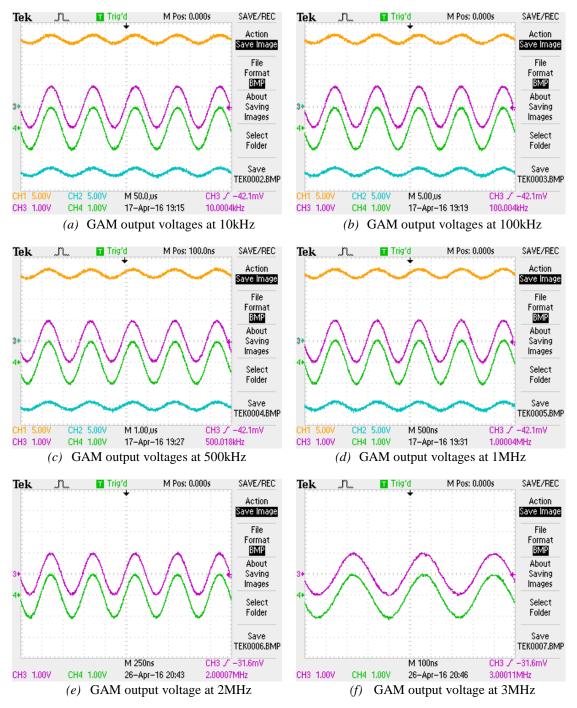

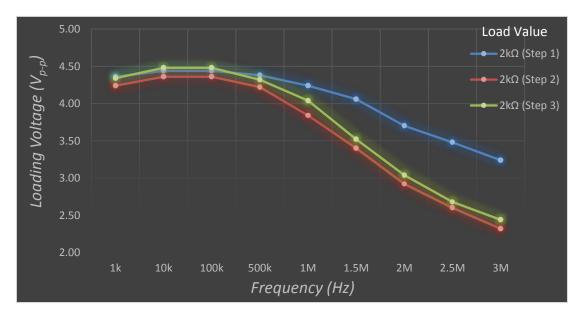

| Figure 7.10: Maximum loading amplitude measured at different frequencies for $2k\Omega$ loading | 3205 |

| Figure 7.11: Maximum loading voltage at respective tested frequencies                           | 206  |

| Figure 7.12: Voltage source SNR at different frequencies                                        | 207  |

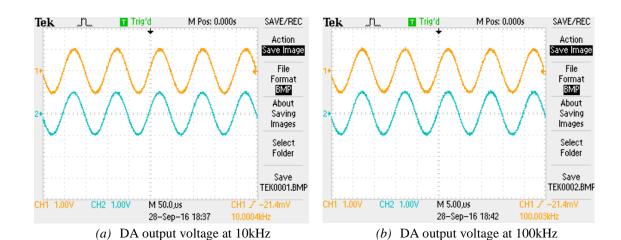

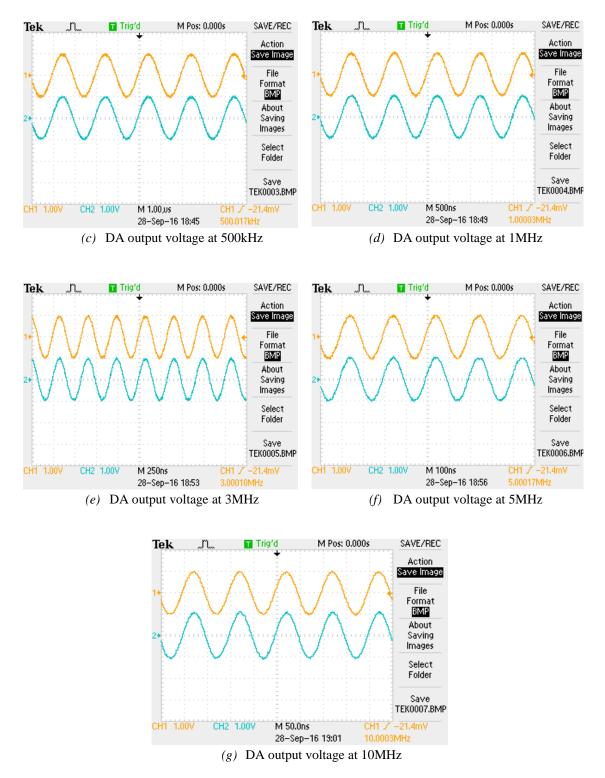

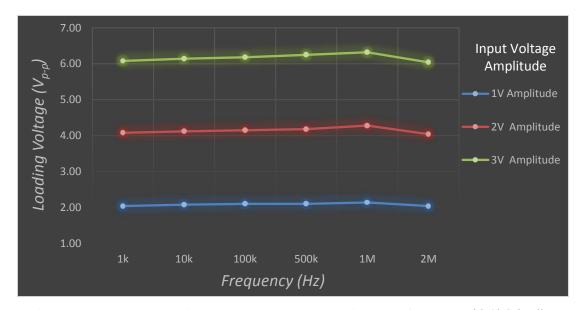

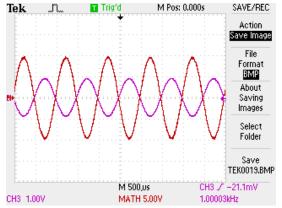

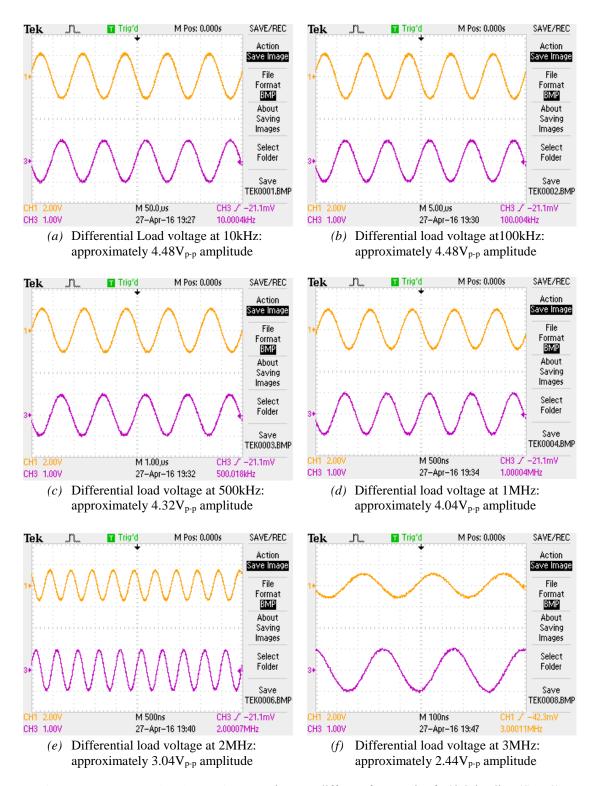

| Figure 7.13: DA Output voltage using $2V_{p-p}$ input at different frequencies                  | 209  |

| Figure 7.14: DA output voltage using different input voltages at respective frequency           | 210  |

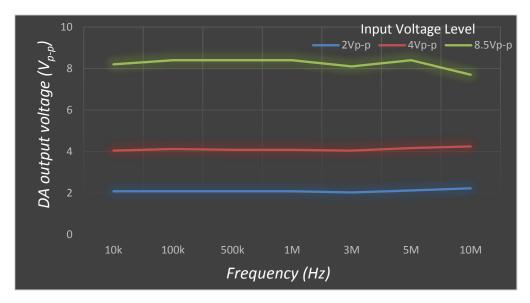

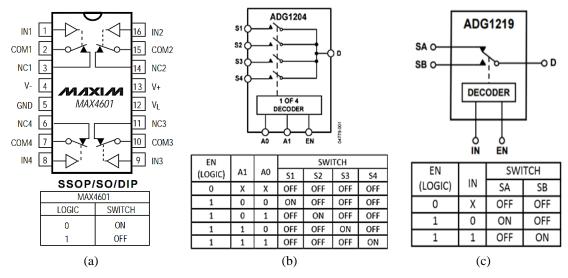

| Figure 7.15: Functional block diagram and logic table of FISM and SMM devices                   | 212  |

| Figure 7.16: The current source PCB.                                                            | 213  |

| Figure 7.17: Power supply schematics for the CSB                                                | 215  |

| Figure 7.18: Board to PC interface schematic                                                    | 216  |

| Figure 7.19: Control interface software for CSB                                                 | 217  |

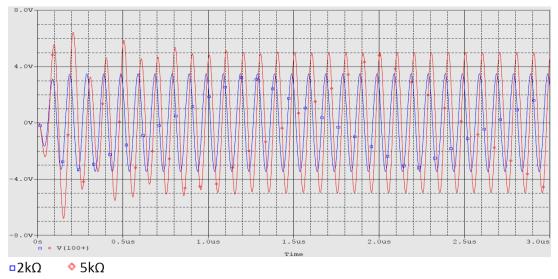

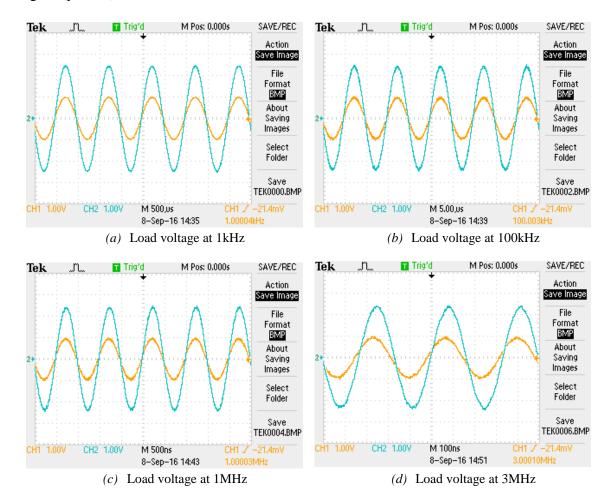

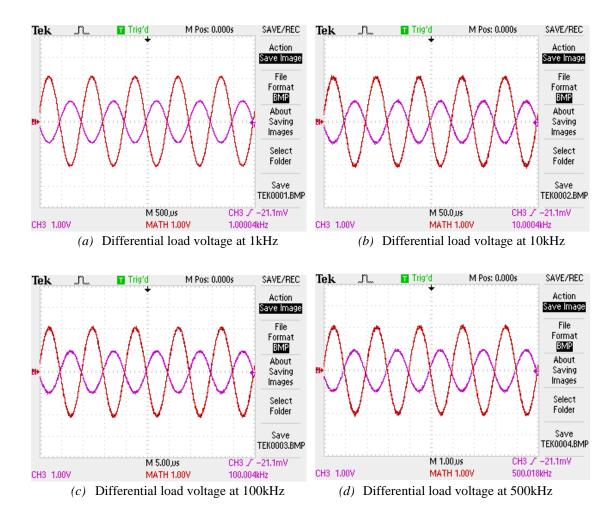

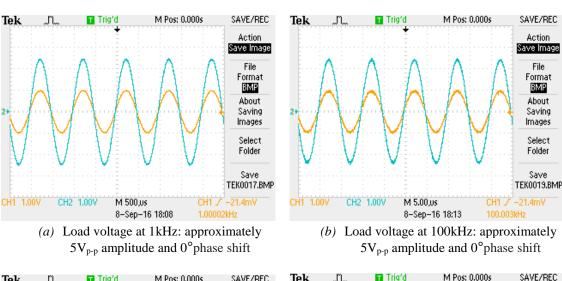

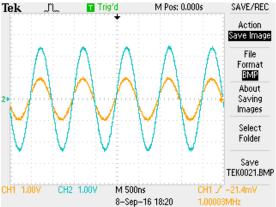

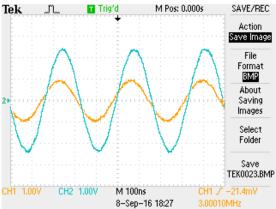

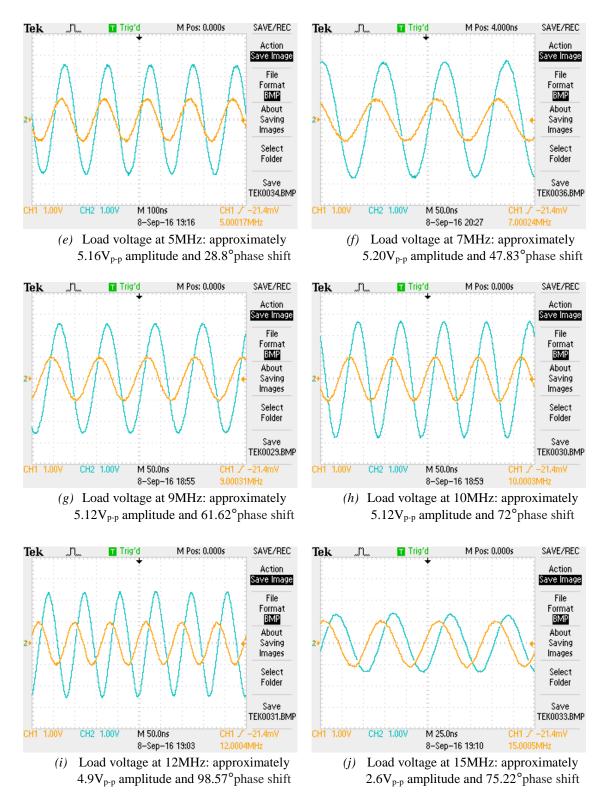

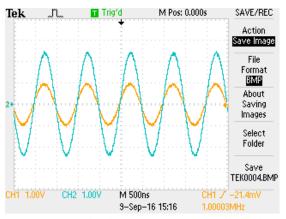

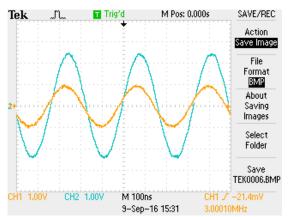

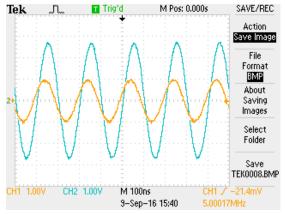

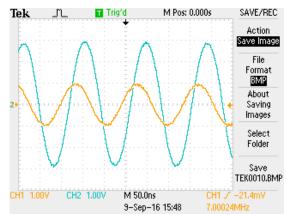

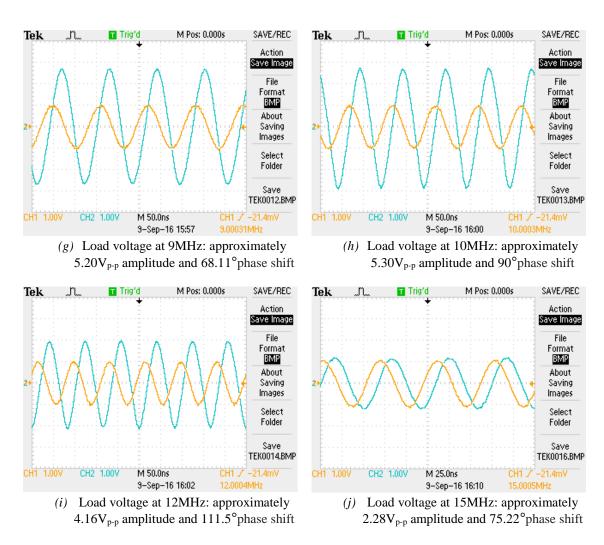

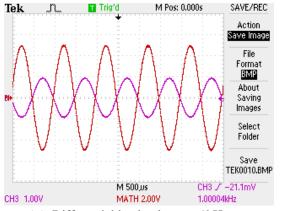

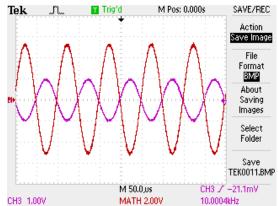

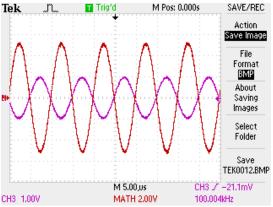

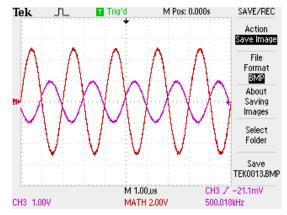

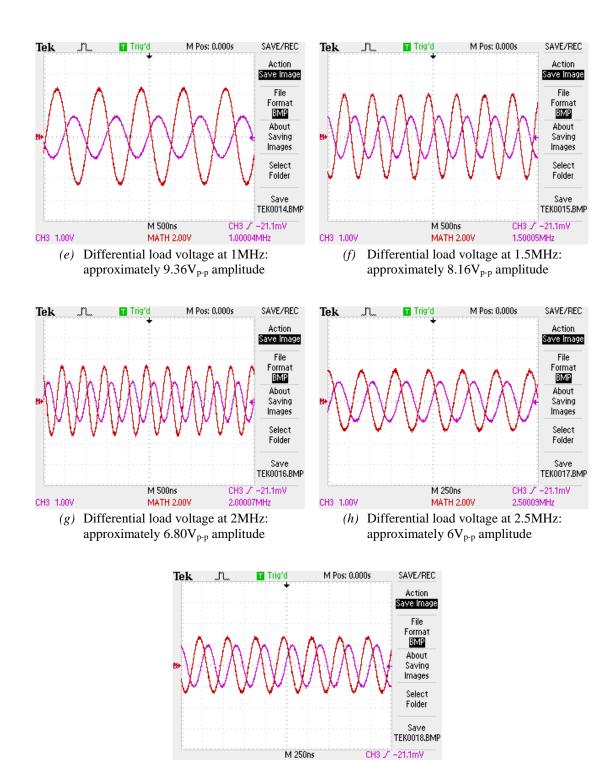

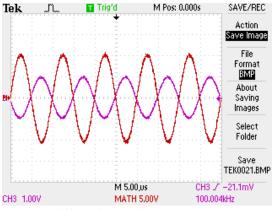

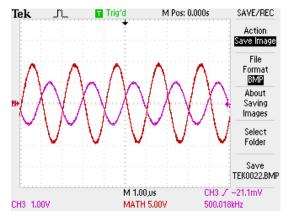

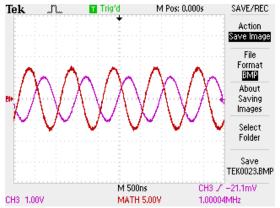

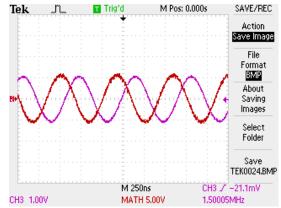

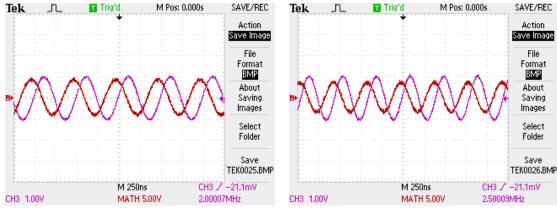

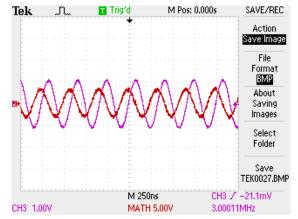

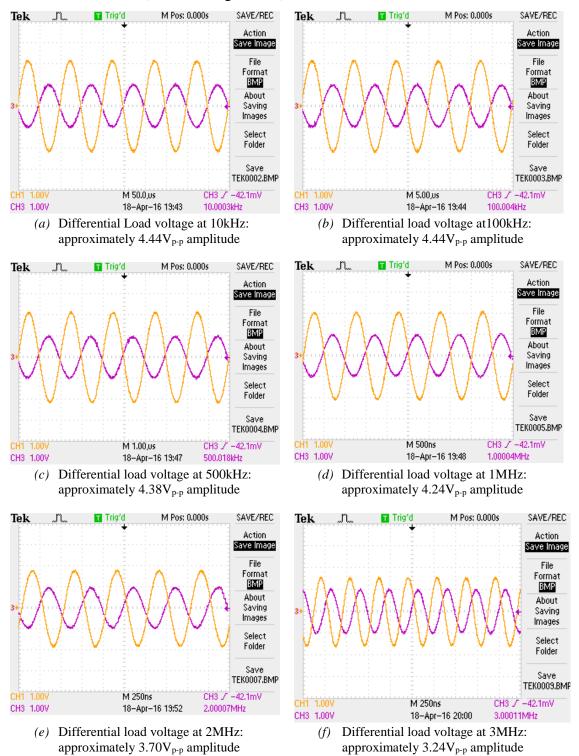

| Figure 7.20: Differential load voltage using $2V_{p-p}$ input at different frequencies          | 219  |

| Figure 7.21: Load voltage frequency bandwidth (-3dB) and phase shift for CSM                    | 220  |

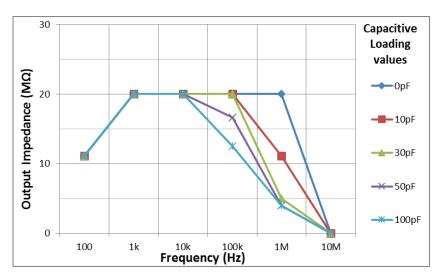

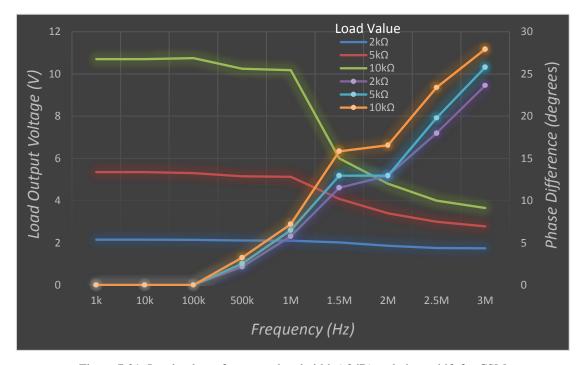

| Figure 7.22: Output & Input Impedance of the CSM at respective tested frequency                 | 222  |

| Figure 7.23: Maximum loading at different tested frequencies                                    | 224  |

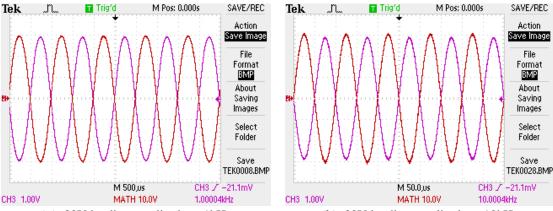

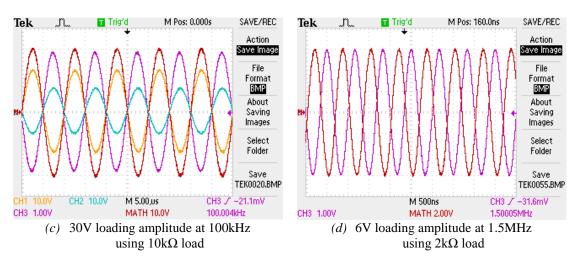

| Figure 7.24: GAM output voltages at different tested frequencies                                | 225  |

| Figure 7.25: Load voltage using CSM and GAM at tested frequency band with $2k\Omega$ loading    | 226  |

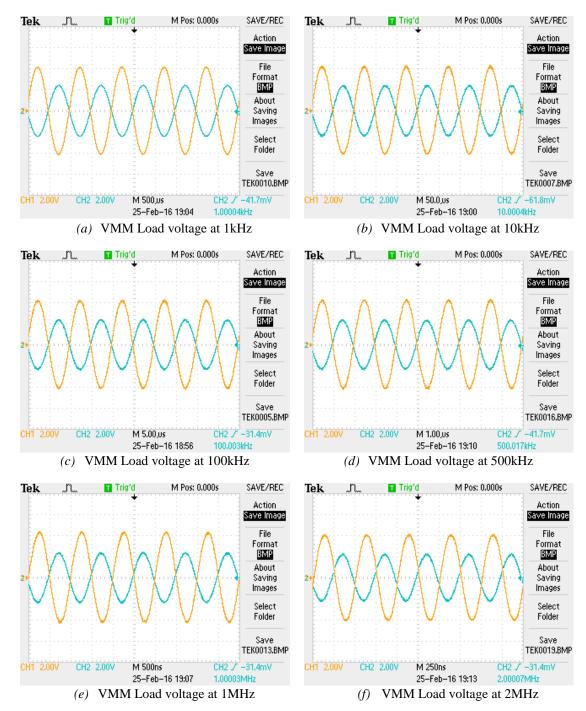

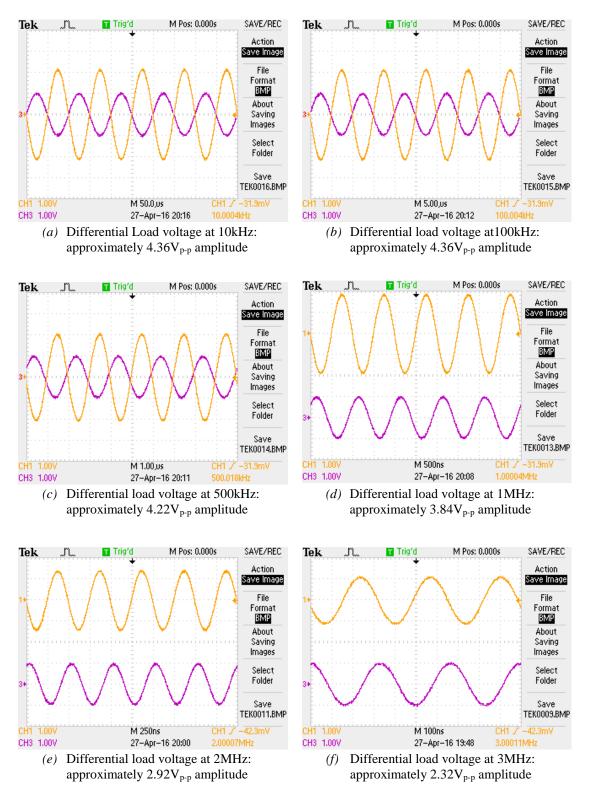

| Figure 7.26: VMM Load voltages measured at different tested frequencies                         | 228  |

| Figure 7.27: Load Voltage using CSM and VMM at respective tested frequency with $2k\Omega$ load | ding |

| against variable input amplitude                                                                | 229  |

# List of Tables

| Table 3.1: Sussex MK4 system specifications (Béqo et al., 2010)                                     |

|-----------------------------------------------------------------------------------------------------|

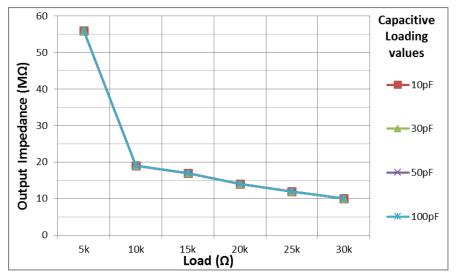

| Table 5.1: Bootstrapped EHCS-GIC Circuit Frequency Bandwidth Response with 10pF loading capacitance |

|                                                                                                     |

| Table 5.2: Output impedance of Bootstrapped EHCS-GIC Circuit with 10pF loading capacitance          |

|                                                                                                     |

| Table 5.3: Output impedance of Bootstrapped EHCS-GIC Circuit with 30pF loading capacitance          |

|                                                                                                     |

| Table 5.4: Output impedance of Bootstrapped EHCS-GIC Circuit with 50pF loading capacitance          |

|                                                                                                     |

| Table 5.5: Output impedance of Bootstrapped EHCS-GIC Circuit with 100pF loading capacitance         |

|                                                                                                     |

| Table 5.6: Bipolar bootstrapped EHCS-GIC circuit frequency bandwidth response with 10pF             |

| loading capacitance                                                                                 |

|                                                                                                     |

| Table 5.7: Output impedance of bipolar bootstrapped EHCS-GIC circuit with 10pF loading              |

| capacitance                                                                                         |

| Table 5.8: Output impedance of bipolar bootstrapped EHCS-GIC circuit with 30pF loading              |

| capacitance                                                                                         |

| Table 5.9: Output impedance of bipolar bootstrapped EHCS-GIC circuit with 50pF loading              |

| capacitance146                                                                                      |

| Table 5.10: Output impedance of bipolar bootstrapped EHCS-GIC circuit with 100pF loading            |

| capacitance                                                                                         |

| Table 5.11: Bandwidth and Output impedance Response of DCCS at 10MHz frequency 154                  |

| Table 6.1: Voltage Source Circuit Initial Frequency Bandwidth Response                              |

|                                                                                                     |

| Table 6.2: Bipolar Bootstrapped Voltage Source Circuit Bandwidth at corresponding RC loading        |

|                                                                                                     |

| Table 6.3: Output impedance of Bipolar Bootstrapped Voltage Circuit with corresponding loading      |

| capacitance                                                                                         |

| Table 6.4: Phase shift of Bipolar Bootstrapped Voltage Circuit with corresponding loading           |

| capacitance                                                                                         |

| Table 6.5: SNR of Bipolar Bootstrapped Voltage Circuit at corresponding loading capacitance         |

|                                                                                                     |

# Chapter 1

# A General Review of Cancer and its Diagnosis Methodologies

#### 1.1 Introduction

Cancer is one of the major medical problems and cause of mortality in the world. Every year, 1-in-250 men and 1-in-300 women is diagnosed cancer. The incidence rises steeply with age so that over the age of 60, 3-in-100 men develop this disease every year. The diagnosis and investigation for this disease is costly and requires a time consuming and labour-intensive treatment. Mostly lung, breast, skin, gut and prostate gland cancers are common in the western world (Coleman et al., 2004; Parkin et al., 2005). Early and reliable cancer detection can deliver substantial health and benefits in the society. This has attracted many researchers around the world, who are contributing to cancer research.

The overall aim of this research work is to design and implement hardware, which will enhance the performance of an Electrical Impedance Tomography (EIT) /Bio-Impedance (BI) system and enable it to become a reliable cancer detection system. The survival rates can be increased by detecting cancer at an early stage. The detection system based on EIT technology provides an opportunity to detect an early stage cancer using a non-invasive method. The detection system's reliability depends on many factors and one of them is the quality of the measuring excitation signal source. The precise focus of this research work is to study the areas related to the improvement of the excitation source followed by the development of a precise and reliable signal excitation system having low noise interference, high frequency bandwidth and capable of driving higher loads. Different analogue circuit architectures for the excitation source have been designed in this research work. The designed excitation sources will have the ability to operate at frequencies between 1kHz to 5MHz. To assess the precision of the generated signal, a printed circuit board (PCB) was implemented with possible load patterns along with high amplitude

voltage measurement circuitry. This provides an opportunity to test the performance of the designed excitation sources for any impedance measurement system. In our case, the successful testing of the excitation source will lead the source circuitry to be integrated into our EIT breast cancer system for clinical application.

The aim of this chapter is to briefly describe the overview of cancer and its related terminologies. The chapter will firstly introduce the cancer and its types followed by the cancer staging, its importance and method to determine staging. This chapter will also describe the diagnosis methods for cancer detection in general. The primary focus of this research work is on breast cancer detection; therefore, the diagnosis methods used for breast cancer detection will also be presented in this thesis. Finally, the chapter will present the research objectives and achievements of this thesis along with thesis organisation.

#### 1.2 What is Cancer?

A collection of related diseases can be termed as Cancer and it starts in our body cells. These cells together make up our body tissues and organs. Usually, the cells divide into new cells in a controlled way when the body requires them. Cancer is developed when the growth of cells is uncontrollable and it begins to produce abnormal cells. These abnormal cells keep on dividing and eventually form a lump, which is called a tumour. Not all tumours are cancerous. A lump can be tested to see whether it is cancerous or not, by extracting a small tissue or cell sample from the lump and examining it using a microscope. The tumour which is not cancerous is called benign which may grow but doesn't spread into nearby tissues. Sometimes it can be large but usually causes problems when it puts pressure on nearby organs. However, when removed they usually don't grow again. The cancerous tumour is called malignant and can spread into nearby tissues. This tumour can sometimes spread from the point it is started (primary) to other parts of the body through the blood or lymphatic system and may begin to grow and form another tumour. This is known as secondary cancer or metastasis. The lymphatic system helps to protect our body from infection and diseases. It drains lymph fluid from body tissues. This system is made up of tubes (lymphatic vessels) which connect to groups of the lymph nodes inside the body. Lymph nodes/glands are a small bean shape, which filter bacteria and disease from lymph fluid.

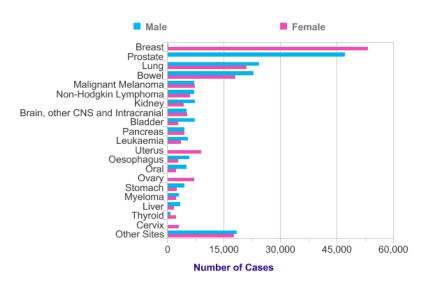

Some of the UK statistics and information during last few years on cancer incidence, mortality and survival are presented. Statistics show that around 352k new cancer cases occurred in 2013 that gives ≈960 cases diagnosed per day. The ratio of diagnosed cancer in males (179k) was higher than females (173k). The overall contribution of certain cancer types (Breast, prostate, lung and bowl) are 53% of the total new cases in 2013. According to 2011-2013 survey, 50% of the cancer diagnosis were in people aged >70 years (Cancer Research UK, 2013b). Statistics further show that around 163k death cases occurred due to lung, bowel, breast and prostate cancer which is almost 46% of the death rate in 2014 (Cancer Research UK, 2014). Survival rate of cancer shows that 50% of cancer diagnosis cases in England and Wales survive their disease for  $\geq 10$  years (2010-11). The survival rate is higher in females as compared to males and has been improved in last 40 years in the UK (Cancer Research UK, 2011). The 20 most common cancer incidences in the UK during 2013 are shown in Figure 1.1. The analysis shows that the most common cancer in the UK is breast cancer, which accounts for 15% to the total cases. Other most common cancers account for 13% (prostate & lung) and 12% (bowel) to the total cases in the UK.

Figure 1.1: Most common cancers incidence in the UK (Cancer Research UK, 2013a)

#### 1.2.1 Types of Cancer

There are many types of cancer and usually identified by the name of the organs or tissues from where it generates. The cell type (epithelial or squamous cell) can also describe

Cancer. This section describes the main types of cancer that begin in specific types of cells.

#### 1.2.1.1 Carcinoma

Carcinoma is the most common type of cancer that usually forms a solid tumour. It is formed by epithelial cells and begins in the skin or tissues, which covers the surface of internal organs and glands. There are many types of epithelial cells, which have a specific name for the corresponding carcinoma.

- Adenocarcinoma is the cancer created in the epithelial cell, which produces

fluids or mucus. Tissues made up of these cells are mostly called glandular tissues.

Breast, colon and prostate are classified as adenocarcinomas.

- Basal cell carcinoma is the cancer that begins in the lower layer of epidermis (outer layer of skin).

- **Squamous cell carcinoma** is the cancer formed in squamous cell, which lies under the outer surface of the skin. These cells also exist in many other organs: stomach, lungs, bladder, intestines and kidneys.

- Transitional cell carcinoma is the cancer formed in epithelial tissue (transitional epithelium). This tissue is made up of many epithelial cell layers and is found in the lining of the bladder, ureters, parts of kidneys and few other organs. Some cancers of these organs are transitional carcinomas.

#### 1.2.1.2 Sarcoma

Sarcoma is the type of cancer that is formed in the bones and tissues that support and connect the body. It can develop in muscles, fat, nerves, joints, blood or lymph vessels and fibrous tissue. The most common cancers of this type are: Osteosarcoma (bones), Kaposi sarcoma, malignant fibrous histiocytoma (soft tissue's) etc.

#### 1.2.1.3 Leukaemia

Leukaemia is the type of cancer that is formed in blood-forming tissue of bone marrow. It begins when healthy blood cells change, grow uncontrollably and usually don't form a solid tumour. Its types are grouped on the basis of: 1) How quickly disease get worse (acute or chronic) and 2) the type of the blood cell started in (lymphoblastic or myeloid).

#### 1.2.1.4 Lymphomas

Lymphomas is the type of cancer, which is formed in the cells of lymphatic system (lymphocytes: T cells or B cells). Lymphocytes are white blood cells that help in fighting against infection and disease. Abnormal lymphocytes build up in lymph nodes and vessels as well as in other body organs represents the existence of this cancer. Lymph tissue can be found throughout the body, as a result this cancer can begin anywhere. It is of two main types: Hodgkin and Non-Hodgkin. Mostly lymphomas are non-Hodgkin, only 1:5 are Hodgkin. Hodgkin has a specific appearance under a microscope and contains Reed Sternberg cells (B-lymphocyte) which become cancerous. Non-Hodgkin doesn't contain Reed Sternberg cells and has a different appearance under the microscope. It has >60 disease types that behave in different ways. It can be formed from B/T cells and can grow slowly or quickly. Both lymphomas can start at any lymph node of the body, but the most common place for its existence is in the neck.

Apart from these types, there are so many different types of cancer, which are difficult to describe in detail and is beyond the scope of this thesis. Detailed type of cancers can be found at: www.cancerresearch uk.org/about-cancer/type.

#### 1.2.2 Cancer Staging and Grading

When a cancer is diagnosed, it is important to know its stage (size of a tumour) and grade (growth level). This information helps to decide regarding cancer treatment. During the initial cancer diagnoses, tests are carried out to check the cancer size and whether it has spread into surrounding tissues or another part of the body. To know the stage of the disease, the patient has to go through diagnosis tests or procedures, which are explained later in this chapter. The question may arise, why cancer staging is important? Staging helps in deciding the level of treatment required by the patient. If the cancer is at one place, then a local treatment (surgery or radiotherapy) is sufficient for that particular area of the body. If the cancer has spread then a treatment that circulates throughout the whole body (systemic treatments) is required. Sometimes the lymph nodes near the cancer are checked to assess the possibility of cancer spreading to another part of the body. If cancer cells are found in these nodes then it is an indication that cancer has begun to spread and requires adjuvant treatment (i.e. surgery followed by chemotherapy) with an intension to kill any cancerous cell, which have spread away from primary tumour location.

The cancer staging system can be mainly divided into two types to classify the malignant tumours: The TNM staging system and the Number staging system.

#### 1.2.2.1 The TNM Staging System

The TNM staging system is widely used in cancer diagnosis. This system provides information using three parameters: T (Primary Tumour), N (Regional Lymph Nodes) and M (Distant Metastasis). It uses numbers to specify: the size of the initial cancer, whether it has spread to the lymph nodes and the possibility of it spreading to a different part of the body. A brief explanation of each parameter is described:

- T refers to the size of the cancer and extent the cancer is spread into its surrounding tissues. It is presented by: X (Tumour can't be measured), 0 (Tumour can't be found) and from 1 (small) to 4 (large) tumour. The scale can be further divided to provide more detailed information e.g. T2a and T2b.

- N refers to the possibility of the cancer cell found in nearby lymph nodes and is represented by: X (can't measure cancer) and between 0 (no cancer cell) to 3 (Number and location of node containing cancer cell).

- M refers to the possibility that the cancer has shifted to another part of the body. It can be represented by: X (Metastasis can't be measured), either 0 (not shifted) or 1 (shifted).

- The letter "p" and "c" used before TNM represents the pathological and clinical stage respectively. Letter "p" and "c" refers to the stage based on tumour examination in the laboratory after cancer removal surgery and the cancer information before surgery (physical examination and test reports) respectively.

#### 1.2.2.2 The Number Staging System

This system uses the TNM system to divide the cancer into stages. Most of the cancers have four stages (1 to 4). The general stages for most of the cancers are briefly described here with a detailed breast cancer staging in section 1.3.2.

- **Stage 1:** This refers to a relatively small tumour, which is contained inside the primary location organ.

- **Stage 2:** This refers to the state in which cancer has not started spreading to the surrounding tissue but the size of tumour is larger than the stage 1 tumour. In this

- stage, it can be assumed that sometimes the cancer cells have spread to the lymph node, which are closely located to the tumour.

- **Stage 3:** This refers to the state in which the size of cancer is large and it may has started to spread into nearby tissues with a presence of cancer cell in lymph nodes in the respective region.

- **Stage 4:** This refers to the state in which the cancer cells have spread from its initial location to another part of the body (metastatic cancer).

Another staging system, which is used for all types of cancer groups and is classified into five non-numeric categories as: In situ, localized, regional, distant and unknown.

#### 1.2.2.3 Cancer Cell Grading

Cancer cell grading is also an important parameter during diagnosis. It gives the information of how quickly the cancer might grow and is based on the appearance of the cancer cell compared to the normal cell under the microscope. It also helps in the post-surgery treatment. The grading can be categorized as:

- **Grade 1:** The cancer cell's appearance is identical to normal cells and usually has slow growth and less chances to spread into the surrounding tissue.

- **Grade 2:** The cancer cells appearance is abnormal and has a slightly faster growth rate.

- **Grade 3:** The cancer cells appearance is totally different from normal cells and has faster growth rate.

# 1.3 Breast Cancer and its Stages

#### 1.3.1 Breast Cancer

An uncontrollable growth of the cells in the breast is an indication of breast cancer. It is mainly related to women's breast but has a possibility to begin in men too. The breasts are composed of: fat tissues, gland tissues divided into lobes and milk ducts. It can start from any part of the breast but mostly it begins in the ducts which carry milk to the nipple (duct cancer) and in the glands, which make milk (lobular cancer). It is not necessary that every type of breast cancer make a lump. It may have any of these signs of cancer: entire

or partly breast swelling, skin irritation, pain in breast/nipple, nipple retraction or discharge, redness/thickness of nipple/breast skin or in armpit lymph node/around collarbone. An important aspect is that most of the breast lumps are benign which don't spread outside the breast. However, some benign lumps can increase the risk to grow towards cancer and should be regularly monitored. Breast cancer can also spread through the lymph system. This is done if cancerous cells have entered the lymph vessels and started growing in the lymph nodes. Once spread to lymph nodes, the cancerous cells have higher chances to spread to other parts of the body and is termed as invasive breast cancer (ductal and lobular). The other type, which stays within the tissue at its primary location without any involvement with surrounding tissues, is termed as in-situ or non-invasive (ductal and lobular). Each type is briefly described:

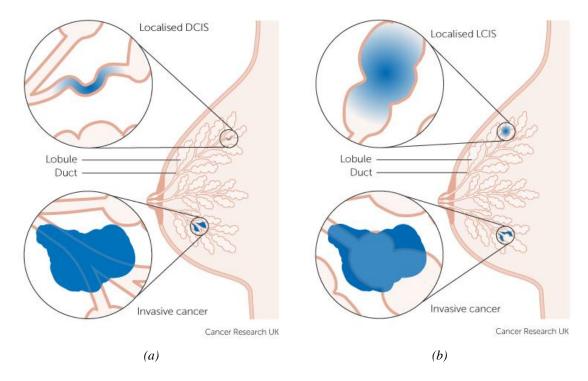

**Ductal Carcinoma in-situ** (**DCIS**): It refers to the uncontrollable cells growth specifically in milk ducts without external spread and is considered as an early cancer stage often identified in a mammography scan. It usually doesn't form a lump but may cause breast pain or nipple discharge and can be dangerous if left untreated. It has a tendency of 25-50% to shift into an invasive type within 10 years. About 1:5 new cases (USA) and around 4800 cases (UK) are diagnosed of this type of breast cancer each year (American Cancer Society, 2016; Cancer Research UK, 2016).

**Lobular Carcinoma in-situ (LCIS):** It refers to the growth of abnormal cells inside the breast lobules and is not identified in a mammography scan due to being symptom less. The cells are often present in the inner lining of the both breast lobules and diagnosed unintended during a biopsy for any other purpose. The existence of LCIS still give risk of being invasive and spreading of breast cancer in either breast over the next few years (1:5 in 15 years). It is diagnosed in about ≈525 women in the UK every year (Cancer Research UK, 2015a).

**Invasive Ductal Carcinoma (IDC):** It refers to the growth of cancerous cells in milk duct (primary location) and spreads into the fatty tissue of the breast by breaking the duct wall. It has an ability to further spread to other parts of the body through the lymph system and blood. IDC has the ratio of 8:10 in the diagnosed invasive breast cancer.

**Invasive Lobular Carcinoma (ILC):** It refers to the growth of cancerous cells in the lobules (primary location) and spreads into other body parts. It is most common in women aged between 45-55 years. Almost a 1:3 ratio of the ILC diagnosis will result in breast

cancer without proper treatment. Its existence is not always in the form of lump, and can appear as a hard/thick breast in the region between armpit and nipple. The ratio of ILC from the diagnosed breast cancer is 1:10.

There are also some less common types of breast cancer, which includes inflammatory breast cancer, nipple Paget disease, phyllodes tumour and angiosarcoma.

Figure 1.2: a) Localised and invasive DCIS cancer b) Localised and invasive LCIS cancer (Cancer Research UK, 2016 & 2015a).

#### 1.3.2 Breast Cancer Stages

As stated earlier, the main scope of the research work presented in this thesis is based on breast cancer detection using the EIT system. Therefore, it is important to describe the detailed cancer stages of the breast so that a precise measurement can be acquired by the EIT system. It is divided into four number stages. Often stage 1 & 2, 3 and 4 are referred to as early breast cancer, locally advanced breast cancer and metastatic breast cancer respectively. The breast cancer stages with detailed tumour size and extent of its spread is described as (Cancer Research UK, 2015b):

**Stage 1:** This stage is further divided into two sub-stages as:

- **Stage 1A:** In this stage, the tumour is <2cm and has not spread to the nearby lymph nodes and outside the breast.

- **Stage 1B:** In this stage, the tumour is not seen in the breast and few cancer cells exist in the lymph nodes in armpit or the tumour is <0.2cm with few lymph nodes in armpit.

#### **Stage 2:** This stage is divided into two sub-stages as:

- Stage 2A: In this stage, the possibilities are: 1) the tumour is <2cm and the lymph nodes in armpit are affected, 2) the tumour is >2cm but <5cm and lymph nodes in armpit are not affected, 3) No tumour is seen but 1-3 lymph nodes in armpit or near breastbone contain cancer cells.

- **Stage 2B:** In this stage, the tumour is >2cm but <5cm along with existence of cancer cells in the lymph nodes in armpit or near the breastbone, or the tumour is >5cm without any affected lymph nodes in the armpit.

#### **Stage 3:** This stage is divided into three sub-stages as:

- **Stage 3A:** In this stage either: 1) no tumour, 2) tumour >2cm but <5cm, 3) tumour >5cm is seen and 4-9 lymph nodes in armpit or near the breastbone are affected.

- Stage 3B: In this stage, the tumour is fixed to the skin or chest wall with: 1) no cancer cells in armpit's lymph nodes, 2) up to 9 lymph nodes in armpit or near the breastbone are affected.

- Stage 3C: In this stage, the tumour can be of any size and has spread to ≥10 lymph nodes in armpit and near the breastbone or to the nodes above and below the collarbone.

**Stage 4:** In this stage, the tumour can be of any size. The lymph nodes may or may not be affected with cancer but it has spread to other organs. If the cancer is only found in, lymph nodes under the arm than it can't be considered as stage 4 breast cancer.

# 1.4 Cancer Diagnosis Method

Different methods have been introduced to diagnose cancer. Advancement and more awareness in cancer research work around the world, has resulted in the development of new diagnostic tools and improvement of the existing methods that help to detect cancer.

If the cancer is suspected, the patient has to go through some tests for diagnosis (by pathologists and imaging radiologist). A second opinion regarding cancer diagnosis is highly recommended. Some types of cancer (lymphomas) may be difficult to classify even by an expert doctor. Hence establishing the exact cancer type and size allows the physician to choose the most effective treatment for the patient. The most common diagnostic methods are:

**Biopsy:** In this procedure, a small sample of tissue is removed and examined under a microscope. Depending upon the location, sometime this test can be performed on an outpatient by giving local anaesthesia. Imaging diagnosis tests, (i.e. X-rays) are helpful in detecting the areas or masses of the abnormality but if used alone it can't differentiate between cancerous and non-cancerous cells. Therefore, to make a definite diagnosis, a biopsy is performed for closer examination. A biopsy can be of various types:

- Bone marrow Biopsy: This type of biopsy is used if an abnormality is detected

in blood or suspect that it has transferred to the bone marrow. This procedure

is used to diagnose many blood problems (both cancerous and non-cancerous).

During this procedure, a sample of bone marrow is taken out from the back of

hipbone using a long needle.

- Endoscopic Biopsy: In this procedure a thin flexible plastic tube with a camera on the end, is used to observe the structure inside the organs and body. The tube can be inserted through mouth, rectum, urinary tract or a small skin cut. Specialized tools are passed through the tube to take a sample of tissue for analysis. Examples are: cystoscopy (bladder tissue sample), bronchoscopy (lung tissue sample), colonoscopy (colon sample) etc.

- Needle Biopsy: In this procedure, a special needle is used to extract suspicious cells from the affected region. It is often used on the outer region of the skin (e.g. suspicious breast lumps etc.). It can be combined with imaging procedures to collect a sample from the region, which can't be felt through the skin. This procedure includes fine needle aspiration, core needle biopsy, vacuum assisted biopsy, image guided biopsy and surgical biopsy.

**Laboratory Tests:** Low and high levels of certain substances (tumour markers) in the body can indicate the probability of cancer. Hence, laboratory tests of the blood, urine or

other body fluid used to measure those substances can be helpful in the diagnosis process e.g. a higher level of prostate specific antigen in the blood indicates the existence of prostate cancer. It is an important diagnosis tool but it should not be independently considered for conclusive cancer diagnosis decision because abnormal laboratory test results are not a guarantee of the cancer existence and other methods should be used to confirm its presence.

Imaging Diagnostic: In imaging diagnosis, pictures of internal areas of the body are produced to see the existence of the tumour. This procedure is significant because it is used as an initial guide to reach a decision before executing any surgery or biopsy procedure. The images are taken by a trained technician and analysed by a radiologist or physician to interpret the diagnostic images. There are many imaging techniques used for cancer diagnosis. These include: X-rays, Computerized axial tomography (CAT/CT) scan, Magnetic resonance imaging (MRI) scan, Ultrasound scan, Positron imaging test (PET) scan and Electrical Impedance Tomography/Mammography (EIT/EIM) for various parts of the body. A comprehensive description of imaging diagnosis techniques is presented in section 1.5.

## 1.5 Imaging Based Cancer Diagnosis

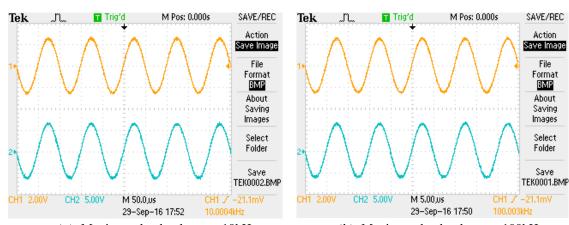

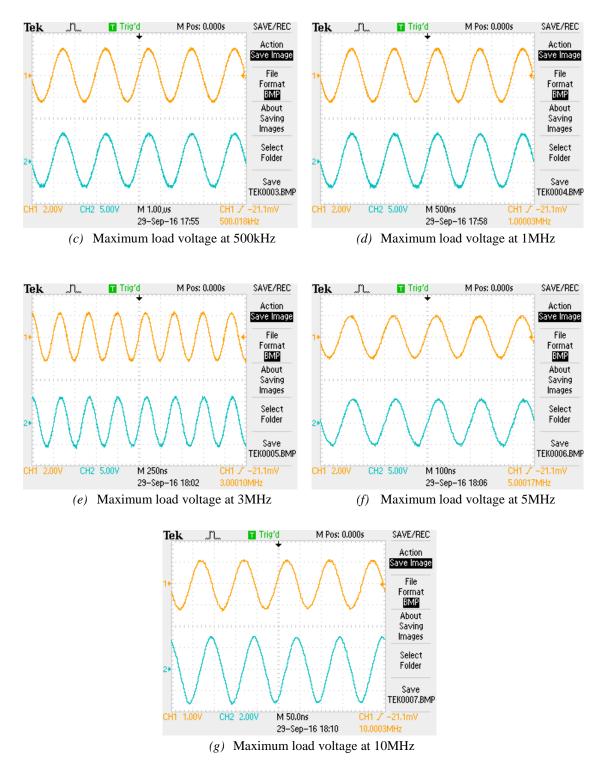

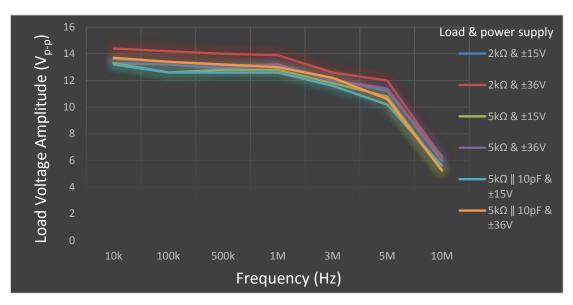

Early cancer detection plays an important role in the survival rate of the patient. Early diagnosis significantly relies on the imaging diagnosis procedures at the screening stage. Imaging and surgical procedures assist each other during the diagnosis process. Biopsy samples provides the stage of the cancer while the imaging procedure provides the location of the cancer region in the designated part of the body. According to the scope of this thesis, the imaging procedures described in this section will focus on breast cancer detection. At the early stage of the breast cancer, the uncontrolled growth of the cells is not started properly and remains with the primary tissue. Hence, the localized cancer can be removed without resorting to the breast removal. There are many different imaging techniques to detect breast cancer. Some of them are being used in medical treatments, whilst others are still in the research and development stages. Each technique has its advantages and disadvantages; therefore, a trade-off needs to be done on the best achievable performance by each technique.